Bachelor Thesis Herbstsemester 2018

# Inhaltsübersicht

*Muen on ARM* Version: 1.00, Datum: 21. Dezember 2018

> Betreuer: Prof. Dr. Andreas Steffen MSc Adrian-Ken Rüegsegger MSc Reto Bürki

> > HSR, Rapperswil

David Loosli, Student BSc Informatik HSR Rapperswil

## Dokumentationsübersicht

- A. Eigenständigkeitserklärung (deutsch)

- B. Persönlicher Bericht (deutsch)

- C. Aufgabenstellung (englisch)

- D. Management Summary (englisch)

- E. Bachelor Thesis (englisch)

- F. Glossar und Abkürzungsverzeichnis (englisch)

- G. Projektorganisation inklusive Zeiterfassung und Protokolle (deutsch)

- H. Studienarbeit (englisch)

- USB Stick mit sämtlichen Daten der während der Bachelor Thesis erstellten Dokumente, dem gesamten Code Repository sowie der referenzierten Literatur (sofern in pdf Form frei erhältlich)

## Eigenständigkeitserklärung

Ich erkläre hiermit,

- dass ich die vorliegende Arbeit selber und ohne fremde Hilfe durchgeführt habe, ausser derjenigen, welche explizit in der Aufgabenstellung erwähnt ist oder mit dem Betreuer schriftlich vereinbart wurde,

- dass ich sämtliche verwendeten Quellen erwähnt und gemäss gängigen wissenschaftlichen Zitierregeln korrekt angegeben habe,

- dass ich keine durch Copyright geschützten Materialien (z.B. Bilder) in dieser Arbeit in unerlaubter Weise genutzt habe.

Tischinas Ruschein, 21. Dezember 2018

Unterschrift David Loosli

Bachelor Thesis Herbstsemester 2018

# Persönlicher Bericht

*Muen on ARM* Version: 1.00, Datum: 21. Dezember 2018

> Betreuer: Prof. Dr. Andreas Steffen MSc Adrian-Ken Rüegsegger MSc Reto Bürki

> > HSR, Rapperswil

David Loosli, Student BSc Informatik HSR Rapperswil

### Ausgangslage

Das Ziel der Bachelor Arbeit war die Implementation eines minimalen Separationskernels für die ARMv8-A Architektur basierend auf den Erkenntnissen der Studienarbeit. Als Zielplattform wurde in einem separaten Evaluationsprozess das NXP LS1012A FRDM Board festgelegt.

### Projektorganisation

Den Erfahrungen bezüglich des administrativen Aufwandes aus der Studienarbeit entsprechend und nach Rücksprache mit sämtlichen Beteiligten entschied ich mich dafür, die Anzahl der verwendeten Projektadministrationstools von deren vier auf zwei zu reduzieren. Neben dem auf einer von der Hochschule für Technik Rapperswil (HSR) zur Verfügung gestellten virtuellen Maschine installierten Software Entwicklungstool Jira von Atlassian konnte über den Server der beiden Betreuer zusätzlich ein Git Repository verwendet werden. Sowohl das Aufsetzen der virtuellen Maschine inklusive der Installation der Jira Software als auch die Konfiguration des Git Repositorys verliefen ohne Probleme. Von beiden Instanzen wurden zusätzlich lokal weitere BackUps erstellt.

Die Betreuung der Arbeit wurde wiederum von Adrian-Ken Rüeggsegger und von Reto Bürki übernommen. Mit dieser war ich auch während der gesamten Bachelor Arbeit äusserst zufrieden. So konnte ich dank einem hervorragend präsentierten Code Walk Through durch den Muen SK Quellcode und der jederzeit vorhandenen Unterstützung bei Schwierigkeiten auch fachlich enorm von diesem Projekt profitieren. Die vollumfänglich protokollierten Besprechungen empfand ich wiederum sowohl auf fachlicher als auch persönlicher Ebene als sehr lehr- und hilfreich. Ich möchte mich deshalb an dieser Stelle nochmals für die Unterstützung bedanken!

Ebenfalls noch ganz herzlich bedanken möchte ich mich bei Prof. Dr. Andreas Steffen. Ohne seine fachliche und organisatorische Unterstützung wäre ein solches, mehrere im Rahmen des Bachelor Studiengangs an der Hochschule für Technik Rapperswil (HSR) zu absolvierende Arbeiten umfassendes Projekt schlichtweg nicht möglich gewesen.

#### **Bachelor Thesis**

Im Gegensatz zum evaluativen Ansatz der Studienarbeit war die Bachelor Arbeit aufgrund der klaren Vorgaben und Erkenntnisse aus der vorangegangenen Studie sehr viel zielgerichteter. Grundsätzlich folgte die Implementation der einzelnen Komponenten dem Aufbau der Studienarbeit.

Obwohl mir seitens der Betreuer erneut viele Freiheiten bezüglich der Herangehensweise an die Problemstellung gewährt wurden, waren die Rahmenbedingungen und Ziele einiges enger gesteckt und wurden auch eingehender überprüft als in der Studienarbeit. Allerdings fehlte es deshalb nicht an Herausforderungen bei der Implementation der einzelnen Komponenten - insbesondere das Generieren der Adresstabellen, bei denen schon die kleinsten Änderungen zu trotz vorhandenem Hardware Debugger kaum sinnvoll zu untersuchenden Fehlern führen können, stellte mich vor so einige Probleme.

PersoenlicherBericht.pdf

Mit dem Ergebnis meiner Bachelor Thesis bin ich persönlich sehr zufrieden. Besonders stolz bin ich auf das Setup der Entwicklungsumgebung mit dem in die GPS IDE von AdaCore integrierten Debug Möglichkeiten über den J-Link Debug Adapter, die angepasste Version der OpenOCD Anwendung und den GDB Debugger Tools. Der einzige kleine Wermutstropfen findet sich darin, dass die Virtualsierungserweiterung des Generic Interrupt Controllers und damit einhergehenden der ARM Generic Timer aus zeitlichen Gründen nicht mehr implementiert werden konnten. Dies insbesondere deshalb, da ich davon überzeugt bin, dass auch diese Komponenten noch hätten realisiert werden können, wäre ich nicht 1.5 Wochen gesundheitlich angeschlagen gewesen. Trotzdem bin ich davon überzeugt, dass sich die rund 580 investierten Stunden in diese Bachelor Arbeit mehr als nur gelohnt haben.

### Persönliche Erkenntnisse

Im Verlaufe des gesamten Projektes konnte ich erneut auf fachlicher Ebene in den verschiedensten Bereiche enorme Fortschritte erzielen und mich bezüglich der administrativen Arbeiten vollumfänglich auf meine bisherigen Erfahrungen aus den anwaltlichen Tätigkeiten verlassen. Ich bin immer noch davon überzeugt, dass mir eine solche Arbeit im Gegensatz zu den üblichen Modulprüfungen ein Vielfaches an konzeptionellem, breit anwendbarem Wissen vermitteln kann.

Während der Bachelor Arbeit konnte ich von den Erkenntnissen der Studienarbeit sehr profitieren. So konnte ich mich dank der Einschränkung der administrativen Arbeiten zugunsten inhaltlicher Aspekte verstärkt mit der eigentlichen Implementation auseinandersetzen. Ich bin der Ansicht, dass sich dies sehr positiv auf die Qualität meines Quellcodes ausgewirkt hat.

Die aus der Studienarbeit gewonnene Erkenntnis bezüglich der Problematik der Einzelarbeit hat sich auch während der Bachelor Thesis bestätigt. So wäre ich in den verschiedensten Situationen froh gewesen, einen Diskussions- und Entscheidungspartner mit einem ähnlichen Wissensstand zu haben. Andererseits könnte sich in Zukunft der Entscheid, eine Einzelarbeit einzureichen, doch noch als lohnenswert herausstellen.

Mitunter eine der wichtigsten Erkenntnisse der Studienarbeit waren die negativen Folgend meiner mit einem zu grossen Aufwand und Perfektionismus verbundenen Herangehensweise. Ich habe diese Erkenntnis während des gesamten Projektes zu berücksichtigen versucht und einen etwas pragmatischeren Ansatz gewählt. Allerdings zeigte sich beispielsweise bei der Implementation des Generic Interrupt Controller, dass mir dies nicht immer gelang und dass ich daran weiter arbeiten muss.

Zum Schluss möchte ich noch anmerken, dass ich das grosse Interesse an meiner Bachelor Arbeit seitens von AdaCore und den Klienten der codelabs GmbH als äusserst motivierend empfand. Ich bin sehr glücklich darüber, dass das Projekt nicht in einem Aktenschrank in Vergessenheit gerät, und freue mich bereits heute auf den Antritt der offerierten Stelle zur Weiterentwicklung des Muen SK on ARM Projektes!

PersoenlicherBericht.pdf

Bachelor Thesis autumn semester 2018

# **Definition of Task**

*Muen on ARM* version: 0.00, date: December 21, 2018

> supervisors: Prof. Dr. Andreas Steffen MSc Adrian-Ken Rüegsegger MSc Reto Bürki

> > HSR, Rapperswil

David Loosli, student BSc in Computer Science HSR Rapperswil

## Introduction

The Muen Separation Kernel (SK) is a specialised microkernel developed as a platform for high-security systems at the University of Applied Sciences Rapperswil (HSR). Muen ensures a strict and reliable isolation of components and protects critical security functions against unreliable software running on the same physical system. The programming language SPARK 2014 is used to achieve a particularly high degree of trustworthiness. The Muen SK was developed specifically for the Intel x86/64 architecture and uses the Intel VT-x and VT-d technology to separate the components.

Based on the findings of the former student research study "Muen On ARM - an Evaluation" written by the author of this Bachelor Thesis, the objective of this study is to develop a minimal Separation Kernel prototype for the ARMv8-A architecture based on the Muen SK and leveraging the AArch64 Virtualization Extensions introduced with the latest ARM architecture. The target hardware platform for this Bachelor Thesis is the NXP LS1012A Freedom Evaluation Board with an ARMv8 Cortex-A53 CPU and the programming language is Ada/SPARK 2014.

## Objectives

- (i) Prototypical implementation of main Separation Kernel building blocks

- System initialization

- Exception & interrupt handling

- Definition and switching of AArch64 subject state

- Subject preemption mechanism

- Serial debug driver

- (ii) Documentation

- (iii) Optional:

- Scheduling of multiple subjects

- AArch64 pagetable generation tool

Bachelor Thesis autumn semester 2018

# **Management Summary**

*Muen on ARM* version: 1.00, date: December 21, 2018

> *supervisors:* Prof. Dr. Andreas Steffen MSc Adrian-Ken Rüegsegger MSc Reto Bürki

> > HSR, Rapperswil

David Loosli, student BSc in Computer Science HSR Rapperswil

## Introduction

The Muen Separation Kernel (SK) is a specialised microkernel developed as a platform for high-security systems at the University of Applied Sciences Rapperswil (HSR). Muen ensures a strict and reliable isolation of components and protects critical security functions against unreliable software running on the same physical system. The programming language SPARK 2014 is used to achieve a particularly high degree of trustworthiness. The Muen SK was developed specifically for the Intel x86/64 architecture and uses the Intel VT-x and VT-d technology to separate the components.

## Background

Based on the findings of the former Student Research Study "Muen On ARM - an Evaluation" written by the author of this bachelor thesis, the objective of this study was to develop a minimal separation kernel prototype for the ARMv8-A architecture based on the Muen SK, written in Ada/SPARK and leveraging the AArch64 Virtualization Extensions introduced with the latest ARM architecture. The target hardware platform for this bachelor thesis is the NXP LS1012A FRDM Board with an ARMv8-A Cortex-A53 single core CPU.

### Results

Using a Segger J-Link hardware debug probe device, the on-chip debugger software OpenOCD and the AdaCore toolchain including their integrated development environment, essential parts of a separation kernel have been implemented in Ada in the course of the project. With this basic separation kernel prototype and its two differently configured subjects, it could be demonstrated that all requirements with respect to the porting of the Muen SK to the ARMv8-A architecture can be met applying the already during the Student Research Study examined ARMv8-A architecture design principles.

## Prospects

Due to the enormous economic interest in porting the Muen SK to the ARMv8-A architecture and the current success of the Muen SK project, the author of this study is going to continue to develop the Muen on ARM project full time starting in March 2018.

Bachelor Thesis autumn semester 2018

# **Bachelor Thesis**

Muen on ARM version: 1.0, date: December 21, 2018

> supervisors: Prof. Dr. Andreas Steffen MSc Adrian-Ken Rüegsegger MSc Reto Bürki

> > HSR, Rapperswil

David Loosli, student BSc in Computer Science HSR Rapperswil

# **Change History**

| date         | version | change                                                                               | author       |

|--------------|---------|--------------------------------------------------------------------------------------|--------------|

| Dec 10, 2018 | 0.1     | prepared template, setup basic version, glos-<br>sary, bibliography and introduction | David Loosli |

| Dec 13, 2018 | 0.2     | bibliography, glossary, abstract and introduc-<br>tion up to scope                   | David Loosli |

| Dec 14, 2018 | 0.3     | introduction up to first part theoretical back-<br>ground                            | David Loosli |

| Dec 15, 2018 | 0.3     | second part theoretical background                                                   | David Loosli |

| Dec 16, 2018 | 0.4     | first part practical part                                                            | David Loosli |

| Dec 17, 2018 | 0.4     | second part practical background                                                     | David Loosli |

| Dec 18, 2018 | 0.4     | third part practical part                                                            | David Loosli |

| Dec 19, 2018 | 0.5     | last part practical part up to epilogue                                              | David Loosli |

| Dec 20, 2018 | 0.6     | change history                                                                       | David Loosli |

| Dec 21, 2018 | 1.0     | final check before hand in                                                           | David Loosli |

## Abstract

The Muen Separation Kernel (SK) is a specialised microkernel developed as a platform for high-security systems at the University of Applied Sciences Rapperswil (HSR). Muen ensures a strict and reliable isolation of components and separates security critical functions against unreliable software running on the same physical system. The programming language SPARK 2014 is used to achieve a particularly high degree of trustworthiness. The Muen SK was developed specifically for the Intel x86/64 architecture and uses the Intel VT-x and VT-d technology to separate the components.

This bachelor thesis implements the main building blocks of a separation kernel for the ARMv8-A architecture, leveraging in particular the recently introduced AArch64 Virtualization Extensions. This practical study builds on the findings of the Student Research Study "Muen on ARM - an Evaluation"also written by the author of this paper that investigated the theoretical and practical aspects of porting the Muen SK to the ARMv8-A architecture. The target hardware platform chosen for this study is the NXP LS1012A FRDM Board.

## Contents

| Cł | nange | e Histo  | ry                                 | 2  |

|----|-------|----------|------------------------------------|----|

| At | ostra | ct       |                                    | 3  |

| 1  | Intro | oductio  | on                                 | 6  |

|    | 1.1   | Struct   | ure of the Thesis                  | 7  |

|    | 1.2   | Scope    | 9                                  | 7  |

|    | 1.3   | Relate   | ed Documents                       | 8  |

|    | 1.4   | Literat  | ture                               | 8  |

| 2  | The   | oretica  | Il Background                      | 10 |

|    | 2.1   | Muen     | Separation Kernel                  | 10 |

|    |       | 2.1.1    | Functional Principle               | 10 |

|    |       | 2.1.2    | Components                         | 11 |

|    | 2.2   | ARM      | Overview                           | 12 |

|    |       | 2.2.1    | ARMv8-A Architecture               | 13 |

|    |       | 2.2.2    | ARM Cortex-A53 Implementation      | 15 |

|    |       | 2.2.3    | ARM Peripheral Components          | 16 |

|    | 2.3   | NXP L    | _S1012A Evaluation Board           | 16 |

|    |       | 2.3.1    | Overview                           | 17 |

|    |       | 2.3.2    | Documentation                      | 19 |

|    |       | 2.3.3    | Board Setup                        | 19 |

| 3  | Prac  | ctical P | Part                               | 22 |

|    | 3.1   | Develo   | opment Environment                 | 22 |

|    |       | 3.1.1    | Toolchain                          | 22 |

|    |       | 3.1.2    | Integrated Development Environment | 23 |

|    |       | 3.1.3    | Debugger Setup                     | 24 |

|    |       | 3.1.4    | Deployment                         | 29 |

|    | 3.2   | Softwa   | are Architecture                   | 30 |

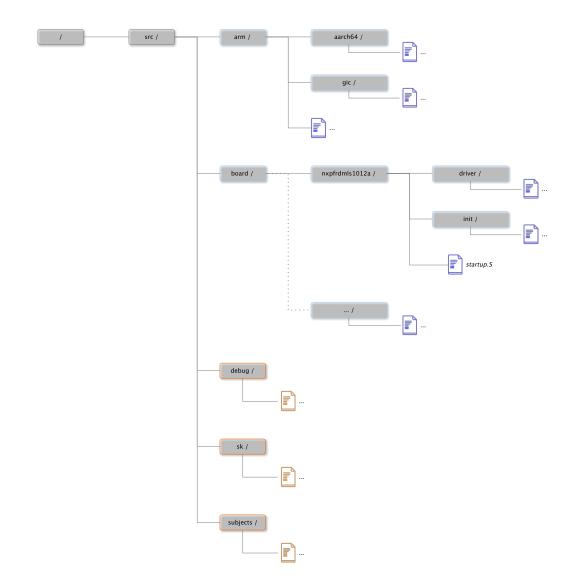

|    |       | 3.2.1    | MuenSK Projects                    | 31 |

|    |       | 3.2.2    | Code Structure                     | 32 |

|    |       | 3.2.3    | Code Style                         |    |

|    |       | 3.2.4    | License                            | 34 |

|    | 3.3   | Impler   | mentation Details                  | 35 |

|    |       | 3.3.1    | Startup Code                       | 35 |

|    |       | 3.3.2    | Registers                          | 36 |

|    |       | 3.3.3    | Subjects                           | 38 |

|    |       | 3.3.4    | Subject Context Switch             |    |

version: 1.0

|    |       | 3.3.5   | Memory Management           | <br>43 |

|----|-------|---------|-----------------------------|--------|

|    |       | 3.3.6   | Exception Handling          | <br>46 |

| 4  | Con   | Iclusio | n                           | 47     |

|    | 4.1   | Status  | s of Development            | <br>47 |

|    | 4.2   | Integra | ration of the Muen SK       | <br>47 |

|    | 4.3   | Furthe  | er Development              | <br>48 |

| 5  | Epil  | ogue    |                             | 49     |

| A  | open  | dix     |                             | 51     |

|    | А     | Projec  | ct Task Description         | <br>51 |

|    | В     | List of | f Related Documents         | <br>53 |

|    | С     | U-Boo   | ot Environment Setup        | <br>54 |

|    | D     | GDB I   | Initialisation Script       | <br>55 |

|    | Е     | Codel   | labs Contributors Agreement | <br>57 |

| Bi | bliog | raphy   |                             | 59     |

| Li | st of | Figure  | 25                          | 61     |

| Li | st of | Tables  | 5                           | 62     |

## **1** Introduction

The tremendous progression in the last years in the world of information technology not only led to an enormous increase of mobile devices and into network integrated components, but also to a raised awareness and alertness with respect to network security among companies and people. In particular, the latest political developments not only in Europe <sup>1</sup> but throughout the world show an increased need for security and protection of one's own personality throughout the internet.

Reto Buerki and Adrian-Ken Rueegsegger recognised this need for high-assurance security very early on and designed the Muen Separation Kernel (SK) as their Master Thesis at the University of Applied Sciences Rapperswil (HSR) in the year 2013<sup>2</sup>. The Muen SK basically leverages three principles. The first principle is a mathematically provable secure approach to control the access to sensitive data and was invented with the theory of the Separation Kernel published by John Rushby in a paper presented at the 8th ACM Symposium on Operating System Principles in December 1981<sup>3</sup>. In order to be able to implement such a separation kernel, the programming language SPARK as a second component was chosen, which allows to formally prove the correctness of code. Thanks to developments in the field of processor architecture, the Muen SK was able to be built on the Intel Virtualization Extension as a third component, thereby improving performance and reducing the size of the code.

In the last years, ARM Limited has expanded its primarily on low energy embedded devices focused business strategy to general purpose central processing unit (CPU) architectures with great success. Many small devices, especially mobile devices, currently use an ARM CPU or an ARM based system on chip (SoC). With the latest ARM architecture, the so called ARMv8 architecture <sup>4</sup>, ARM Limited finally introduced a Virtualization Extension composed of several components that opened the market for small devices also to the Muen SK.

After the successful exploration of the ARMv8-A architecture during the Student Research Study and the confirmation that a porting of the Muen SK should be possible, this bachelor thesis as the final paper of the Bachelor of Science in Computer Science program at the University of Applied Sciences Rapperswil (HSR) now realizes the main components of a separation kernel for the ARMv8-A architecture in software. Even though the target platform for this project is the the NXP LS1012A Freedom evaluation board, the implementation attempts - whenever possible - to keep in mind the diversity of the existing ARM based system on chip (SoC).

bachelorthesis.pdf

version: 1.0

<sup>&</sup>lt;sup>1</sup>Exemplarily, the Datenschutz Grundverordnung (DSGVO) established by the European European Union (EU) and put into force since May 2018 can be mentioned with its effects for the entire continent, https://www.nzz.ch/wirtschaft/folgen-der-neuen-datenschutz-grundverordnung-eu... (dt.), December 21, 2018.

<sup>&</sup>lt;sup>2</sup>[2] Buerki and Rueegsegger. *Muen - An x86/64 Separation Kernel for High Assurance*. 2013.

<sup>&</sup>lt;sup>3</sup>[22] Rushby. "Design and Verification of Secure Systems". 1981.

<sup>&</sup>lt;sup>4</sup>https://en.wikipedia.org/wiki/ARM\_architecture#ARMv8-A, December 21, 2018

## **1.1 Structure of the Thesis**

This paper is divided into three main parts preceded by this introduction and followed by an epilogue containing a summary of the project. In the first main part (chapter 2) an overview of the theoretical background related with the topic of porting the Muen SK to the ARMv8-A architecture is given. This includes an overview of the ARM architecture, a description of the chosen hardware platform as well as a short analysis of the Muen SK. The next chapter 3 describes the development and deployment process as well as the software architecture and design decisions that had to be taken during the construction phase of this project. The explanations of this passages of the document correspond - with regard to the content - to the software architecture document (SAD) as an important part of the software development process. The third main part of this thesis (chapter 4) is dedicated to an analysis and discussion of the current implementation and suggests some approaches for further development and the integration of the ARMv8-A project into the Muen SK.

## 1.2 Scope

As already mentioned, the main objective of this study is to develop a minimal separation kernel prototype for the ARMv8-A architecture based on the Muen SK and leveraging the AArch64 Virtualization Extensions introduced with the latest ARM architecture. The official task description document can be found in the appendix A. In order to be able to achieve the corresponding objectives in the time available, the following topics - even though important with respect to the porting of the Muen SK - have to be considered out of scope:

- (i) ARM TrustZone: The ARM TrustZone provides a hardware mechanism to isolate trusted software. With this separation, an ARMv8-A processor supports a secure (Secure World) and a non-secure (Normal World) state and allows an operating system to run in parallel with a so called trusted operating system <sup>5</sup>. Since the ARMv8-A boot process requires the code in the TrustZone to be executed before entering the Normal World over the secure monitor and since the Muen SK as a hypervisor has to be executed at exception level 2 in the non-secure state, the ARM TrustZone is considered to be out of scope for this study. In future, it must be ensured that the ARM TrustZone does not execute any code or at least does not have access to the Normal World.

- (ii) System Initialization: At the beginning of the project it was determined that the firmware and bootloader should in particular configure and initialize the DDR RAM component and hand over execution to the hypervisor code at exception level 2. However, in the course of the project it soon became apparent that the hypervisor has to make additional configurations with regard to the physical interrupt handling <sup>6</sup> and the Generic Interrupt Controller (GIC) <sup>7</sup> at exception level 3.

bachelorthesis.pdf

<sup>&</sup>lt;sup>5</sup>Further details can be found in in chapter 3, section 3.2 in the Student Research Study [4] and on the ARM homepage under https://developer.arm.com/technologies/trustzone, December 21, 2018.

<sup>&</sup>lt;sup>6</sup>cf. chapter 3, section 3.3.1

<sup>&</sup>lt;sup>7</sup>cf. chapter 3, section 3.3.6

Therefore, it is now assumed that the according evaluation board (a) configures and initializes the existing random access memory (RAM) components, (b) establishes an identity mapping as well as configures and enables the Memory Management Unit (MMU) if necessary for the use of the RAM, and (c) hands over the execution to the separation kernel code at exception level 3 (i.e. secure monitor mode). Since this requirements are derived from the currently used NXP LS1012A FRDM evaluation board, this assumptions will have to be extended and adjusted or as well taken to a higher level of abstraction with the integration of further target hardware platforms.

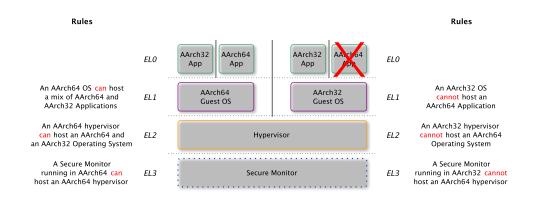

- (iii) ARMv8-A AArch32: As described in the following chapter 2.2, the ARMv8-A architecture retains full compatibility with the ARMv7-A AArch32 execution state. Therefore, there actually exist two sets of registers related with either the AArch64 or the AArch32 execution state. Since the extension of the kernel to the execution of 32-bit applications does not provide any additional conceptual insights, this implementation of a separation kernel only considers the ARMv8-A AArch64 execution state.

- (iv) *Multicore Environment:* This study only considers aspects of a single core system and therefore sets all eventually existing cores apart from the main processor into a waiting state.

## **1.3 Related Documents**

As this bachelor thesis is based on the feasibility study of porting the Muen SK to the ARMv8-A architecture, the Student Research Study written by the author of this paper is declared as an **integral** part of this document. In the following it is therefore assumed that the reader is familiar with the basics of hardware related concepts and software development explained in the student research project. A list of all the related documents can be found in the appendix B.

## 1.4 Literature

First of all, it has to be mentioned that a detailed list of referenced literature can be found in the bibliography at the end of this document (cf. Bibliography). Due to the structure and the requirements of this bachelor thesis, the principal literature used for writing this document as well as the implementation source code can be divided into four different main topics:

(i) ARM: The theoretical part is mainly based on the Student Research Study<sup>8</sup> but also incorporates the book Profession Embedded ARM Development by James A Langbridge<sup>9</sup>. For the practical part with respect to the ARM related literature, both the generic architecture documents with the

<sup>&</sup>lt;sup>8</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017.

<sup>&</sup>lt;sup>9</sup>[3] Langbridge. *Professional Embedded ARM Development*. 2014.

ARMv8-A Programmer's Guide<sup>10</sup> and the ARMv8-A Architecture Reference Manual<sup>11</sup> as well as the documents specifying the implementation of the processor, i.e. the ARM Cortex-A53 MP Core Technical Reference Manual<sup>12</sup>, specific application notes on in-depth topics such as the Virtualization Extension<sup>13</sup> and Generic Interrupt Controller related manuals<sup>1415</sup>, have to be considered.

- (ii) Evaluation Board: For all by the ARM documentation as "implementation defined" declared issues and for all driver related topics, the NXP LS1012A processor specific (i.e. the Data Sheet<sup>16</sup>, the Processor Reference Manual<sup>17</sup> and the Security Reference Manual<sup>18</sup>) and the NXP LS1012A FRDM board specific documents (i.e. Getting Started Guide<sup>19</sup> and the Board Reference Manual<sup>20</sup>) have to be consulted.

- (iii) Muen SK: Although the book Programming in Ada 2012<sup>21</sup> could not be worked through completely due to the time constraints of this bachelor thesis, it has nevertheless to be mentioned at this point as a reference book together with the online available Ada Reference Manual <sup>22</sup>. The implementation also follows the SPARK principles explained in the Muen documentation<sup>23</sup> and the Muen SK design and implementation principles<sup>24</sup>.

- (iv) Development and Tools: As the development environment and the corresponding tools form the basis of the entire project, a separate section is dedicated to them. The principal literature used for this topic includes the OpenOCD User's<sup>25</sup> and Developer's<sup>26</sup> Guides, the Segger J-Link documentation<sup>27</sup>, the ARM Cortex JTAG interface documentation<sup>28</sup> and the NXP PBL Configuration Application Note<sup>29</sup>.

<sup>19</sup>[17] n.a. *QorIQ LS1012A Getting Started Guide*. 2016.

<sup>&</sup>lt;sup>10</sup>[7] n.a. ARM Cortex-A Series, Programmer's Guide for ARMv8-A. 2015.

<sup>&</sup>lt;sup>11</sup>[6] n.a. ARM Architecture Reference Manual - ARMv8, for ARMv8-A architecture profile. 2018.

<sup>&</sup>lt;sup>12</sup>[8] n.a. ARM Cortex-A53 MPCore Processor, Technical Reference Manual. 2018.

<sup>&</sup>lt;sup>13</sup>[5] n.a. AArch64 Virtualization. 2017.

<sup>&</sup>lt;sup>14</sup>[9] n.a. ARM Generic Interrupt Controller, Architecture Specification. 2013.

<sup>&</sup>lt;sup>15</sup>[11] n.a. CoreLink GIC-400 Generic Interrupt, Technical Reference Manual. 2012.

<sup>&</sup>lt;sup>16</sup>[16] n.a. *QorlQ LS1012A Data Sheet.* 2018.

<sup>&</sup>lt;sup>17</sup>[18] n.a. *QorIQ LS1012A Reference Manual.* 2018.

<sup>&</sup>lt;sup>18</sup>[19] n.a. *QorIQ LS1012A Security (SEC) Reference Manual.* 2017.

<sup>&</sup>lt;sup>20</sup>[15] n.a. QorlQ LS1012A Board Reference Manual. 2016.

<sup>&</sup>lt;sup>21</sup>[1] Barnes. *Programming in Ada2012*. 2018.

<sup>&</sup>lt;sup>22</sup>Official Ada 2012 Reference Manual, https://developer.arm.com/technologies/trustzone, December 21, 2018

<sup>&</sup>lt;sup>23</sup>[2] Buerki and Rueegsegger. Muen - An x86/64 Separation Kernel for High Assurance. 2013, SPARK, chapter 2, section 2.1, page 3 f.

<sup>&</sup>lt;sup>24</sup>[2] Buerki and Rueegsegger. *Muen - An x86/64 Separation Kernel for High Assurance*. 2013, Design, chapter 3, page 19 ff., and Implementation, chapter 4, page 31 ff.

<sup>&</sup>lt;sup>25</sup>[21] Oliver et al. Open On-Chip Debugger: OpenOCD User's Guide. 2017.

<sup>&</sup>lt;sup>26</sup>[20] Oliver et al. Open On-Chip Debugger: OpenOCD Developers's Guide. 2017.

<sup>&</sup>lt;sup>27</sup>[13] n.a. J-Link / J-Trace User Guide. 2018.

<sup>&</sup>lt;sup>28</sup>[12] n.a. CoreSight Components, Technical Reference Manual. 2009.

<sup>&</sup>lt;sup>29</sup>[14] n.a. *QorIQ LS1012A Application Note, PBL Configuration using QCVS.* 2016.

## 2 Theoretical Background

This chapter is intended to give a brief overview of the topics already developed in the Student Research Study by summarising the individual chapters of the documentation and highlighting the most important topics once again.

## 2.1 Muen Separation Kernel

As already mentioned, the design and implementation of the Muen SK is premised on three basic concepts. First of all, it is based on the Separation Kernel principle introduced by John Rushby<sup>1</sup> that basically adapts the principles of a distributed system with respect to physical isolation, communication and shared ressources to a single processor and can be verified with a Proof of Separability. Secondly, the theory of the Separation Kernel principle requires that an actual implementation of this principle has to use a programming language that is amenable to formal verification. Therefore, the Muen SK is written in SPARK, a formally analysable subset of the programming language Ada<sup>2</sup>. Finally, to achieve the requirement of a sufficiently small code base, the Muen SK relies on the hardware virtualization support of the Intel x86/64 architecture<sup>3</sup>.

### 2.1.1 Functional Principle

As defined by the separation kernel principle, the system or security policy is at the heart of the Muen SK implementation. This policy describes basically a system-wide, static allocation of resources in a way such that the guest systems are strictly isolated from each other and their communication is exclusively governed by the Muen SK type I hypervisor according to a policy. In practice, this means that supported by the Muen SK Tools an IRQ routing specification for the system's I/O APIC<sup>4</sup>, a vector routing specification to determine the destination subject of interrupt vectors<sup>5</sup>, a memory map defining the kernel stack, the page tables and the per-CPU storage memory addresses, the static scheduling plans for all CPU cores including a barrier as synchronization mechanism to avoid any interprocessor drift in the context of scheduling plans and hence to eliminate timing side channels<sup>6</sup> as well as the subject specifications are generated. Finally, all object binaries created by the build process (i.e. the Muen SK kernel and all subjects) are packed into a bootable OS image<sup>7</sup>.

<sup>&</sup>lt;sup>1</sup>[22] Rushby. "Design and Verification of Secure Systems". 1981.

<sup>&</sup>lt;sup>2</sup>cf. https://www.adacore.com/sparkpro, December 21, 2018

<sup>&</sup>lt;sup>3</sup>[2] Buerki and Rueegsegger. *Muen - An x86/64 Separation Kernel for High Assurance*. 2013, Intel Virtualization Technology (VT), chapter 2, section 2.3.1, page 12 ff.

<sup>&</sup>lt;sup>4</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 2, section 2.3, page 18 ff.

<sup>&</sup>lt;sup>5</sup>[2] Buerki and Rueegsegger. *Muen - An x86/64 Separation Kernel for High Assurance*. 2013, External Interrupts, chapter 4, section 4.4.6, page 50 f.

<sup>&</sup>lt;sup>6</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 2, section 2.2, page 17 f.

<sup>&</sup>lt;sup>7</sup>[2] Buerki and Rueegsegger. *Muen - An x86/64 Separation Kernel for High Assurance*. 2013, Image Packaging, chapter 4, section 4.5.3, page 57 f.

### 2.1.2 Components

The Muen SK makes use of several (hardware) components and principles to guarantee the separation of the guest systems. In this section, the most important components especially with respect to this bachelor thesis are mentioned again. Detailed descriptions of these components and principles can be found in the Student Research Study in chapter 2.

To be able to implement a small code based type I hypervisor, the target processor architecture needs to provide hardware assisted virtualisation support. The Muen SK relies on the Intel Virtualization Technology (VT) that introduces a new hypervisor execution level with an additional protection ring and simplifies the switching between a hypervisor running in VMX root operation and a guest subject executing in VMX non-root<sup>8</sup>.

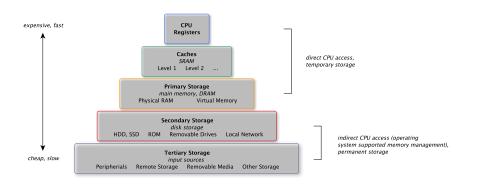

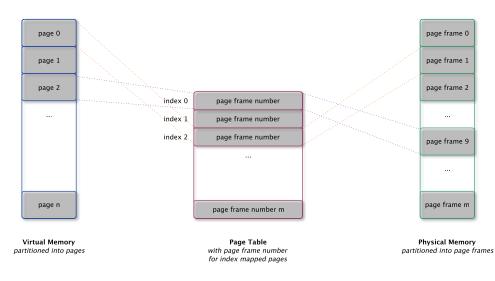

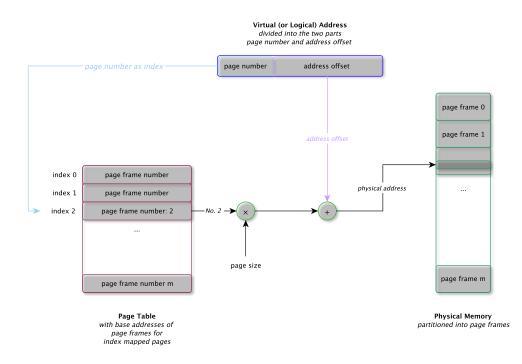

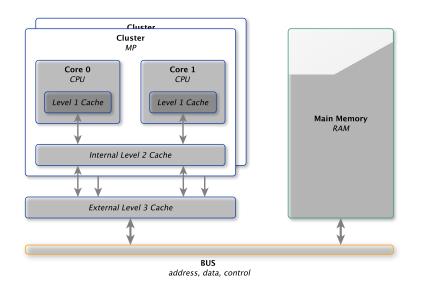

With respect to memory and storage, it is crucial to remember the different technologies within their hierarchy as well as the varying aspects of accessing this components<sup>9</sup>. While the secondary (i.e. disk storage) and tertiary (i.e. input storage) are treated as a pure I/O device by the Muen SK<sup>10</sup>, all memory resources of a system running the Muen SK are allocated statically and are explicitly specified in the so called system policy<sup>11</sup>. This, for example, not only implies that there is no such mechanism implemented for loading missing page contents from a storage device after a page fault or page miss, as most of the common operating system kernels would do, but also leads to the concept of generating the page tables statically during the compilation and build phase of the Muen SK. A detailed overview of the functionality, use and resulting requirements with respect to memory, caches, memory management, advanced memory virtualization and even memory in multicore environments can be found in chapter 2, section 2.2, of the Student Research Study.

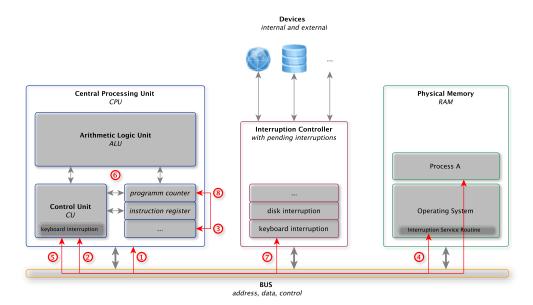

The third aspect that has to be concerned in the context of separating guest systems is the interrupt handling. The Muen SK uses the Intel's Advanced Programmable Interrupt Controller (APIC) that is composed of two components - the Local APIC as a part of every physical CPU and the I/O-APIC as a part of the chipset. This combination of a local and system-wide part provides the possibility not only to forward external interrupts to specific cores but also to create a mechanism that is used for inter-subject signalization. The Muen SK implementation distinguishes between Exceptions, Software Generated Interrupts, Traps and Events. These types of interrupts are then handled differently according to the VMX mode and the subject class. As an example, VM subjects running in VMX non-root mode must implement their own exception handling and hence exceptions and software generated interrupts must not result in a subject exit, whereas an exception occuring during the regular execution of the Muen SK in VMX root mode would indicate a serious problem in the kernel code and hence halt the whole system. Further details, especially related to the handling of the different interrupt types, can, again, be found in the Student Research Study in chapter 2, section 2.3, page 18 and following pages.

<sup>&</sup>lt;sup>8</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 2, section 2.1, page 10 ff.

<sup>&</sup>lt;sup>9</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 2, section 2.2, page 11 ff.

<sup>&</sup>lt;sup>10</sup>[4] Loosli. *Student Research Study, Muen on ARM - an Evaluation.* 2017, chapter 2, section 2.5, page 24 ff.

<sup>&</sup>lt;sup>11</sup>[2] Buerki and Rueegsegger. *Muen - An x86/64 Separation Kernel for High Assurance*. 2013, Memory, chapter 3, section 3.4.2.1, page 24.

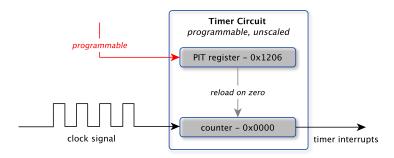

As for every software written for an integrated circuit, the Muen SK also needs a timer to first of all schedule the different subjects but also to be able to implement a system-wide synchronization barrier to avoid any interprocessor drifts<sup>12</sup>. Therefore, the most important timer used by the Muen SK is the VMX preemption timer provided by Intel's virtualization extension that allows the kernel to hand over execution to a subject for a beforehand specified time slice and to return to the hypervisor after the timer has expired in a preemptive way, i.e. regardless of what operations a subject was performing<sup>13</sup>. However, a timer usable for the implementation of the Muen SK must also provide valid accessibility across all cores in order to be able to implement the required system-wide synchronization barrier.

The last important component of the Muen SK implementation is the programming language SPARK, a specialized well-defined subset of the Ada general-purpose language designed for high integrity software. This programming language was chosen by the founder of the Muen SK project due to the ability of SPARK to formally prove the correctness of the software with respect to a variety of program properties before the program is executed. An overview to the possibilities of SPARK can be found the Student Research Study<sup>14</sup> and the book Programming in Ada 2012<sup>15</sup>.

## 2.2 ARM Overview

The Advanced RISC Machines ARM architecture denotes a Reduced Instruction Set Computing RISC microprocessor design by ARM Limited. Due to the focus of the processor architects at ARM Limited on a low number of transistors and hence a low power consumption and heat generation, ARM processors were in the past mainly used in the embedded area. With the ARMv8-A architecture introduced in 2011, ARM Limited has presented its first 64-bit architecture with a virtualization extension not only applicable for embedded systems but also interesting for personal computers and server systems as an alternative to Intel and AMD processors<sup>16</sup>.

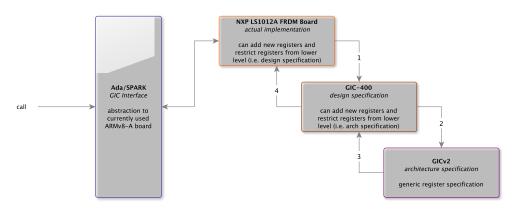

To be able to understand the structure of all the reference manuals and technical documents needed to develop software for a specific ARM system, one has to bear in mind that ARM Limited - in contrast to the popular Intel processors - does not manufacture the processors itself, but grants design licenses to semiconductor manufacturing companies. Due to this licensing strategy of ARM Limited, there exists a large number of different so called ARM-based System on Chip (SoC) that correspond to a combination of an ARM specified processor as CPU together with other peripheral devices and coprocessors. Therefore, the following document structure and development hierarchy have to be considered for developing software for a specific SoC<sup>17</sup>:

bachelorthesis.pdf

version: 1.0

<sup>&</sup>lt;sup>12</sup>[2] Buerki and Rueegsegger. Muen - An x86/64 Separation Kernel for High Assurance. 2013, Scheduling, chapter 3, section 3.4.7, page 29 f.

<sup>&</sup>lt;sup>13</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 2, section 2.4, page 23 f.

<sup>&</sup>lt;sup>14</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 2, section 2.4, page 23 f.

<sup>&</sup>lt;sup>15</sup>[1] Barnes. *Programming in Ada2012*. 2018, chapter 27, section 27.6, page 839 ff.

<sup>&</sup>lt;sup>16</sup>[4] Loosli. *Student Research Study, Muen on ARM - an Evaluation.* 2017, chapter 3, page 29.

<sup>&</sup>lt;sup>17</sup>[3] Langbridge. *Professional Embedded ARM Development*. 2014, chapter 1, page 10 ff.

- (i) ARM Architecture: The highest level of abstraction in the specification of an ARM-based SoC is called the processor architecture. The according Architecture Reference Manual defines all the features common to a family of processor's core designs including the assembly instruction set, the supported processor modes and memory management components. The architecture does not specify the actual core architecture conclusively, but delegates some of properties as "implementation defined" to the ARM core implementation specification. An ARM architecture specification can typically be recognized by the letter "v" in the naming for example, ARMv7 denotes an architecture, while ARM7 stands for an (older) core design specification.

- (ii) ARM Core Implementation: The second highest level of abstraction is the specification of the actual core design. The according Technical Reference Manual gives additional information on the options left "implementation defined" by the ARM architecture version but does not add or explain architectural features in a more detailed way. The latest processor implementation specifications by ARM Limited normally contain the term "Cortex" in their naming as an example, the name Cortex-A15 denotes a core design with an ARMv7 architecture.

- (iii) SoC Specific Components: At the lowest level of abstraction, the SoC manufacturers provide another Reference Manual that contains not only details on the core implementation but also specifies all additional components (i.e. GPU, interrupt controller, etc.) and their usage (i.e. memory mapping of peripheral devices, controller enabling etc.) included in the same integrated circuit, as the accessibility of the processor to the peripherals and its control is not predetermined by ARM. In practice, the SoC manufacturers also often provide fully functional evaluation boards for the software development. Their architecture and implementation details are then usually explained again in a separate Board Reference Manual <sup>18</sup>.

#### 2.2.1 ARMv8-A Architecture

This section basically summarises the ARMv8 fundamentals<sup>19</sup> of the Student Research Study and recapitulates the most important topics in connection with the porting of the Muen SK to the ARM architecture. As already mentioned, ARM Limited not only presented its first 64-bit processor with the introduction of the ARMv8-A architecture, but also added a Virtualization Extension to the processor's architecture. However, the naming is somewhat misleading - the Virtualization Extension is not a single component, but consists of several additional structures on top of already existing components and design principles of the architecture itself. This allows on the one hand to maintain the backward compatibility to the ARMv7-A architecture and on the other hand to support a simplified development of type I and II hypervisors<sup>20</sup>.

<sup>&</sup>lt;sup>18</sup>There are a variety of different SoC and board architectures with different accessibility strategies: from processor controlled (Odroid C2 with amlogic S905 SoC, cf. https://www.hardkernel.com/shop/odroid-c2, December 21, 2018) to CoProcessor controlled (Raspberry Pi 3 with Broadcom 2837, cf. https://www.raspberrypi.org/products/raspberry-pi-3-model-b, December 21, 2018).

<sup>&</sup>lt;sup>19</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 3, section 3.2, page 34 ff.

<sup>&</sup>lt;sup>20</sup>5, cf. for AArch64 Virtualization.

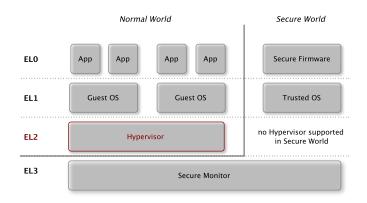

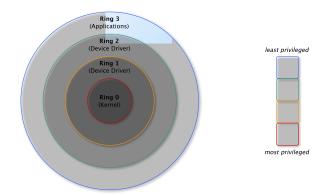

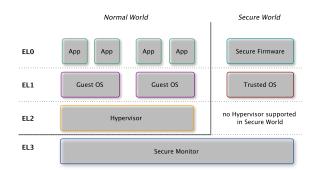

The first and most important aspect of the Virtualization Extension is the additional hypervisor layer with respect to the ARM exception level concept provided at the exception level 2. It is important to note, that, unlike on Intel x86/64 architecture, code execution at a higher Exception Level (i. e. an Exception Level EL*n* with a larger value for *n*) has *more* privileges than code execution at a lower one<sup>21</sup>. In addition to a separated privilege level, the Virtualization Extension provides some hypervisor specific registers for a simplified software development as well as an additional Hypervisor Call instruction HVC as an extension to the ARM64 and ARM32 instruction sets. The additional registers allow, for example, to trap register access and instruction execution in the guest systems to the hypervisor on a per subject base. Further details on the exception level principle and the execution states of the ARMv8-A architecture can be found in the Student Research Study<sup>22</sup>.

Figure 2.1: ARMv8-A Exception Levels in AArch64 with Hypervisor Level

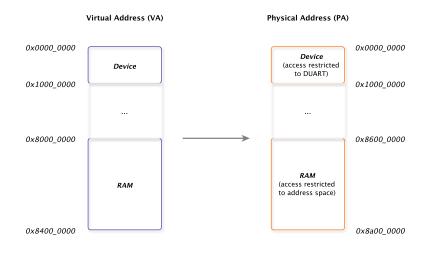

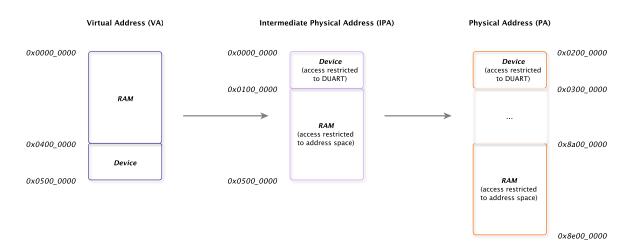

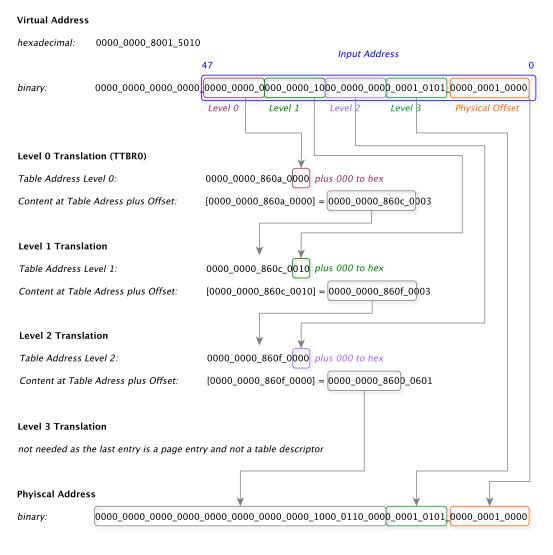

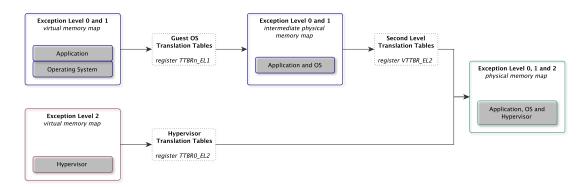

In addition to the in the ARM A architecture standard memory components, i.e. the Memory Management Unit (MMU) as well as the various caches and cache maintenance functions, the Virtualization Extension provides specific virtualisation-related cache maintenance instructions and a second level address translation mechanism (i.e. so-called Stage 2 translation). This allows a type I hypervisor to implement an additional, for a guest system transparent address translation and to create a separate memory mapping for each subject running at the exception levels 1 and 0. For details with respect to the standard and advanced virtualisation memory mechanisms including multicore-related explanations for the ARMv8-A architecture, it is referred to section 3.4 of the Student Research Study.

In the ARM terminology, all interrupts (i.e. external and internal interrupts, system errors, aborts and software generated interrupts) are denoted as exceptions. While at this point a detailed description of the exception handling is omitted and the corresponding sections in the Student Research Study ref-

bachelorthesis.pdf

<sup>&</sup>lt;sup>21</sup>[7] n.a. ARM Cortex-A Series, Programmer's Guide for ARMv8-A. 2015, chapter 3, page 3-1.

<sup>&</sup>lt;sup>22</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 3, section 3.2.1, page 34 ff., and chapter 3, section 3.2.2, page 37 ff.

erenced<sup>23</sup>, the two different possibilities regarding the virtualisation of interrupts have to be mentioned again. Along with the additional Hypervisor Control Register, the ARMv8-A Virtualization Extension provides a simple solution for the virtualisation of exceptions. Due to the design principles used for the Muen SK with its local and system-wide separation of the interrupt handling, this mechanism, however, is not sufficient for the porting of the Muen SK to the ARM architecture. As shown in the course of the Student Research Project, the exception handling has to rely on an additional component also specified by ARM Limited, i.e. the Generic Interrupt Controller starting at version 2 (GICv2)<sup>24</sup>. Since already many of the existing SoC implement an interrupt controller meeting the GICv2 specification, this only slightly restricts the usage of the Muen SK on different ARM-based SoC. Details on the GIC specified by ARM Limited can, again, be found in the Student Research Study<sup>25</sup>.

The last important aspect of porting the Muen SK to the ARMv8-A architecture is the ARMv8-A Generic Timer. Due to the scope of this thesis, the following explanations are restricted to the AArch64 execution state<sup>26</sup>, although the basic timer mechanism are still the same for the AArch32 execution state except for the differently mapped and named registers. Every core design that fulfills the ARMv8-A architecture specification, has to provide at least one SoC-wide system timer, which provides a uniform view of the overall system time. Also mandatory are a memory mapped system counter and a memory mapped virtual timer per core with at least one comparator each, to configure the timers to generate an interrupt when the count is greater or equal to the programmed comparator value (i.e. preemption mechanism). As explained in the Student Research Study<sup>27</sup>, this three timer and counter components already fulfill the Muen SK requirements. But usually, the core specification includes some optional timers and counters for a variety of combinations of secure state, execution state and exception level. The corresponding Technical Reference Manuals (cf. section 2.2.2) give further details on their accessibility. In addition, the SoC manufacturer is free to implement even more timer and counter components (e.g. NXP Flex Timer Modul for the NXP LS1012A FRDM Board).

#### 2.2.2 ARM Cortex-A53 Implementation

As already mentioned and described in the following chapter, the target platform of this bachelor thesis is the NXP LS1012A with an ARMv8-A Cortex-A53 core. Therefore, this section only briefly discusses the Technical Reference Manual for the corresponding core design<sup>28</sup>. Since a comprehensive or even final explanation of the details of the core design compared to the architecture specification is neither possible nor useful, a simple example will be given to provide some insights into the interaction between architecture and core design specification.

<sup>&</sup>lt;sup>23</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 3, section 3.5, page 47 ff.

<sup>24</sup>cf. section 2.2.3

<sup>&</sup>lt;sup>25</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 3, section 3.5.6, page 51 ff.

<sup>&</sup>lt;sup>26</sup>[6] n.a. ARM Architecture Reference Manual - ARMv8, for ARMv8-A architecture profile. 2018, chapter D10, section D10.1, page D10-2645 ff.

<sup>&</sup>lt;sup>27</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 3, section 3.6, page 52 ff.

<sup>&</sup>lt;sup>28</sup>[8] n.a. ARM Cortex-A53 MPCore Processor, Technical Reference Manual. 2018.

When accessing a memory address, the Memory Management Unit checks (among other things), whether the corresponding process has the required access permissions. These access rights can be defined per page level by using the Memory Attribute Indirection Register (MAIR\_EIn). Since this means that only eight different access definitions per exception level can be created by the developer, the architecture specification offers the option of implementing additional access permission definitions with the Auxiliary Memory Attribute Indirection Registers (AMAIR\_EIn). The interpretation and accessibility of these registers are declared as "implementation defined" by the ARMv8-A architecture and therefore left to be specified by the respective core designs<sup>29</sup>. While other core designs implement and specify these registers to be used for additional memory access rights, the ARMv8-A Cortex-A53 now declares this registers as "not implemented" and hence "reserved zero"<sup>30</sup>.

### 2.2.3 ARM Peripheral Components

ARM Limited not only grants architecture and design licenses for processors, but also specifies further (peripheral) components that can be integrated into a System on Chip. Typically, these specifications have exactly the same structure as the documentation of the processors - i.e. at the highest level of abstraction there is an ARM architecture specification, followed by a design specification also developed by ARM Limited and at the lowest level of abstraction the manufacturer of the SoC provides further details on the implementation of the component.

For this study, only two of these peripheral component specifications have to be considered. First, the Generic Interrupt Controller Architecture Specification<sup>31</sup> with the CoreLink GIC-400 Technical Reference Manuel<sup>32</sup> for the exception handling <sup>33</sup> and, second, the CoreSight Components Technical Reference Manual<sup>34</sup> as design specification for the official IEEE-Standard JTAG debug interface <sup>35</sup> to be able to use the hardware debugger <sup>36</sup>.

## 2.3 NXP LS1012A Evaluation Board

In the course of the Student Research Study, it could be showed that the Raspberry Pi 3 is not suitable as a development platform for porting the Muen SK<sup>37</sup>. Therefore prior to this bachelor thesis, several evaluation boards were examined with respect to various requirement criteria, whereby only boards were considered that come with an ARMv8-A processor and could be qualified as "processor con-

<sup>&</sup>lt;sup>29</sup>[6] n.a. ARM Architecture Reference Manual - ARMv8, for ARMv8-A architecture profile. 2018, chapter D12, section D12.2.11, page D12-2705 f.

<sup>&</sup>lt;sup>30</sup>[8] n.a. ARM Cortex-A53 MPCore Processor, Technical Reference Manual. 2018, chapter 4, section 4.3.54, page 4-90.

<sup>&</sup>lt;sup>31</sup>[9] n.a. ARM Generic Interrupt Controller, Architecture Specification. 2013.

<sup>&</sup>lt;sup>32</sup>[11] n.a. CoreLink GIC-400 Generic Interrupt, Technical Reference Manual. 2012.

<sup>&</sup>lt;sup>33</sup>cf. section 3.3.6

<sup>&</sup>lt;sup>34</sup>[12] n.a. CoreSight Components, Technical Reference Manual. 2009.

<sup>&</sup>lt;sup>35</sup>https://de.wikipedia.org/wiki/Joint\_Test\_Action\_Group, December 21, 2018

<sup>&</sup>lt;sup>36</sup>cf. section 3.1

<sup>&</sup>lt;sup>37</sup>[4] Loosli. *Student Research Study, Muen on ARM - an Evaluation.* 2017, chapter 4, page 56 ff.

trolled<sup>«38</sup>. After this evaluation the NXP LS1012A FRDM Board was finally chosen as target platform, although it does not - like all other examined development boards - meet all the technical criteria. The following table 2.3 shows a summary of the results of this evaluation:

| Board            | Cortex-A53 | 64-bit | TrustZone | GIC | SMMU                 | Ada Support 39 | DevTools 40 | Price 41 | AA <sup>42</sup> |

|------------------|------------|--------|-----------|-----|----------------------|----------------|-------------|----------|------------------|

| Pine64 Rock64    | v          | × .    | ×         | ×   |                      | ×              | 7           | 34.95    | HDR Media        |

| Pine A64(+)      | v          | ~      | ×         | ~   | ×                    | ×              | 5           | 29.00    | low cost pc      |

| Odroid C2        | v          | × .    | ×         | × . |                      | ×              | 5           | 46.00    | allrounder       |

| NXP LS1012A FRDM | ~          | ~      | ×         | ~   | ~                    | ×              | 8           | 53.40    | allrounder       |

| Espressobin      | ×          | × .    | ×         | × . | ×                    | ×              | 4           | 79.00    | network          |

| Macchiatobin     | ×          | ~      | ×         | ~   | <ul> <li></li> </ul> | ×              | 6           | 269.00   | network          |

| Jetson TX1       | ×          | ~      | ×         | ~   | ×                    |                | 9           | 582.90   | VC, KI           |

Table 2.1: board evaluation process, final result matrix

### 2.3.1 Overview

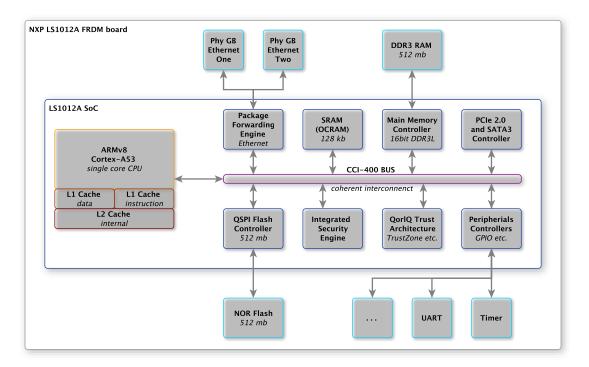

Figure 2.2: NXP LS1012A FRDM evaluation board

The QorlQ LS1012A freedom evaluation board is a low cost development platform for the NXP LS1012A processor series. It is based on a 800 MHz LS1012A ARM Cortex-A53 single processor with 512 mb DDR3L DRAM, a dual 1000Base-T ethernet interface with RJ-45 connectors, USB 2.0 and 3.0 OTG

<sup>39</sup>i.e. additional community edition support and bb-runtime examples

<sup>&</sup>lt;sup>38</sup>[4] Loosli. *Student Research Study, Muen on ARM - an Evaluation.* 2017, chapter 3, page 29, and chapter 4, section 4.1, page 56 f., esp. Figure 4.2: Raspberry Pi 3 schematic.

<sup>&</sup>lt;sup>40</sup>i.e. other development tool independent of the programming language including debugging, example code, documentation etc. with grades between 1 (abysmal) to 10 (brilliant)

<sup>&</sup>lt;sup>41</sup>i.e. price in US Dollar with 2 GB RAM

<sup>&</sup>lt;sup>42</sup>i.e. the application area, the board was designed for

with Micro A/B connectors, a PCIe 2.0 and SATA3 controller, various peripheral interfaces and GPIO connectivity as well as additional debug support via the ARM Cortex 10-pin CoreSight JTAG connector or the CMSIS DAP through a K20 Cortex-M microcontroller. Even though the LS1012A SoC does not feature a System Memory Management Unit (SMMU), the evaluation board was chosen due to the NXP announcements of different i.MX 8 64-bit multi-core SoC with an integrated, the ARM specification fulfilling SMMU<sup>43</sup>. Further details on the features of this evaluation board can be found in the according data sheet<sup>44</sup> as well as online <sup>45</sup>.

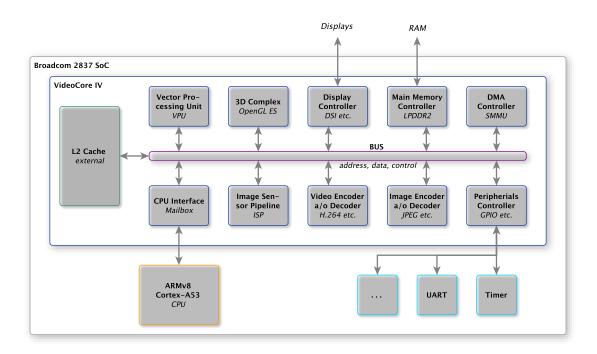

In contrast to the Raspberry Pi 3 board examined in the Student Research Study, the NXP LS1012A FRDM board is a processor controlled evaluation board<sup>46</sup>. This means that the ARMv8-A Cortex-A53 on the NXP evaluation board is the organising part of the SoC and has therefore full control over the initialisation of each component. Figure 3.6 shows a schematic overview for the architecture of the target platform for this study.

Figure 2.3: NXP LS1012A FRDM schematic

<sup>&</sup>lt;sup>43</sup>cf. NXP LS1021A i.MX 8 series https://www.nxp.com/products/.../i.mx-8-processors:IMX8-SERIES, December 21, 2018

<sup>44</sup>[16] n.a. *QorIQ LS1012A Data Sheet*. 2018.

<sup>&</sup>lt;sup>45</sup>cf. for the board specifications https://www.nxp.com/.../qoriq-frdm-ls1012a-board:FRDM-LS1012A, and the SoC details https://www.nxp.com/.../qoriq-layerscape-1012a-low-power-communication-processor:LS1012A, December 21, 2018

<sup>&</sup>lt;sup>46</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 4, section 4.1, page 56 f.

### 2.3.2 Documentation

Another reason, why the NXP LS1012A board was chosen as the target platform for this bachelor thesis, is the detailed and comprehensive documentation as well as the support and development tools provided by NXP. It has to be mentioned that all NXP documents and tools are only accessible by creating a free NXP developer account. Apart from the literature already mentioned in section 1.4, the following tools and support options are then available via the NXP account:

- CodeWarrior IDE: With the as a 30 days test version available CodeWarrior package, NXP not only provides an IDE but also includes some (bare metal) code examples written in assembly and the C programming language <sup>47</sup>. This code examples were used to get a basic understanding of the boot process of the NXP LS1012A Board.

- *QorlQ Linux SDK:* The Linux Software Development Kit (SDK) for QorlQ Processors offers a full-featured development environment consisting of the Linux kernel and device drivers source code, a Yocto Embedded Linux development environment, GNU tools (compilers, linkers, etc.), the adapted U-Boot bootloader source code as well as boot-related firmware, libraries and middleware <sup>48</sup>. This SDK is needed to be able to build a slightly customised U-Boot bootloader that exits at exception level 3 (cf. the following section).

- *Community Forum:* The developer account also grants access to the NXP community forum that is administrated by an NXP support team. In the course of this project, the author also had to rely on this support option <sup>49</sup>.

### 2.3.3 Board Setup

Like almost every development board with an ARM-based SoC, the NXP LS1012A FRDM too has quite an unexpected boot process. As soon as the board is turned on, the firmware initialises all components to their default values, executes the ARM TrustZone Secure Boot bootloader and exits on exception level 3 into the secure monitor. The only boot option available after the firmware initialisation is the QSPI flash memory device<sup>50</sup>. The development boards are delivered with the factory settings for the QSPI Flash as shown in table 2.3.3 and hence start with the pre-boot loader (PBL) composed of the Reset Configuration Word (RCW) and the pre-boot initialisation (PBI) commands. This pre-boot loader not only configures all peripheral devices (e.g. the UART GPIO Pin Mux) but also initialises the DDR3 RAM component on the NXP LS1012A Board<sup>51</sup>. After the pre-boot loader, the U-Boot bootloader is called and initialises the DUART serial communication peripheral to be able load and execute custom ARMv8-A binaries from within the U-Boot console.

bachelorthesis.pdf

<sup>&</sup>lt;sup>47</sup>cf. https://www.nxp.com/.../codewarrior-development-tools:CW\_HOME, December 21, 2018

<sup>&</sup>lt;sup>48</sup>cf. https://www.nxp.com/.../linux-sdk-for-qoriq-processors:SDKLINUX, December 21, 2018

<sup>&</sup>lt;sup>49</sup>cf. https://community.nxp.com/thread/487093, December 21, 2018

<sup>&</sup>lt;sup>50</sup>[17] n.a. *QorIQ LS1012A Getting Started Guide*. 2016, chapter 11, page 11.

<sup>&</sup>lt;sup>51</sup>[14] n.a. *QorIQ LS1012A Application Note, PBL Configuration using QCVS.* 2016, for more details.

| Start Address | End Address | Image                             | Maximum Size |

|---------------|-------------|-----------------------------------|--------------|

| 0x4000_0000   | 0x400F_FFFF | RCW and PBI                       | 1 MB         |

| 0x4010_0000   | 0x400F_FFFF | U-boot boot loader and PFE binary | 1 MB         |

| 0x4020_0000   | 0x401F_FFFF | U-boot environment                | 1 MB         |

| 0x4050_0000   | 0x409F_FFFF | PPA FIT                           | 2 MB         |

| 0x40A0_0000   | 0x43FF_FFFF | Kernel ITB                        | 59 MB        |

Table 2.2: NXP LS1012A QSPI Flash Layout

As already mentioned in the section 1.2, it soon became apparent in the course of the project that the hypervisor has to make additional configurations with regard to the physical interrupt handling <sup>52</sup> and the Generic Interrupt Controller (GIC) <sup>53</sup> at exception level 3. Therefore, the NXP LS1012A Board with its factory settings can not be directly used for running the code developed during this bachelor thesis. Due to the absence of a QSPI Flash driver support in the OpenOCD software, the simplest way to update the evaluation board with a suitable bootloader is as follows <sup>54</sup>:

- (1) Pre-boot loader and U-Boot Binaries: First, the latest Linux SDK for QorlQ Processors has to be downloaded from the NXP software page and installed according to the package installation instructions. Following the build instructions also provided within the package, the latest PBL and U-Boot binaries can then be built. Since the entire build process is relatively complex, the two binaries to be used can be found in the *scripts* folder of the *muensk* project in the directory *u-boot*. Due to the uncertain license situation, it is important to note that the binaries should only be used in the context of this bachelor thesis (i.e. educational use only).

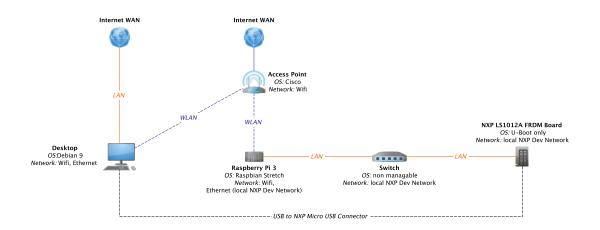

- (2) TFTP Server Setup: In a second step, a TFTP server in a local network has to be set up. For this study, a Raspberry Pi 3 running the official TFTP software (i.e. tttpd-hpa) provided by the Debian-based Raspbian operating system was used. An installation and configuration guide can be found at https://www.cyberciti.biz/faq/install-configure-tftp-server-ubuntu-debianhowto. To be able to load the binaries directly from the development environment on the desktop computer to the TFTP server, an additional FTP server was configured on the Raspberry Pi 3 according to the setup guide published at http://raspberry-projects.com/.../vsftpd-ftp-server. The support scripts for the whole process can also be found in the *scripts* folder of the *muensk* project. The final setup for this project was the following:

<sup>&</sup>lt;sup>52</sup>cf. chapter 3, section 3.3.1

<sup>&</sup>lt;sup>53</sup>cf. chapter 3, section 3.3.6

<sup>&</sup>lt;sup>54</sup> Attention - even though this is the easiest way to update the bootloader, it is still possible to brick the NXP evaluation board by not exactly following the NXP Getting Started Guide or messing up the RCW or PBI binaries. If something went wrong with the update of the code in the flash memory the only option to unbrick the board is to use a JTAG hardware debugger tool with appropriate QSPI flash support.

Figure 2.4: TFTP Server Setup

(3) QSPI Flash Update: Finally, the pre-boot loader and U-Boot binaries have to be uploaded to the TFTP server and written to the QSPI flash memory of the NXP LS1012A FRDM Board. This can be achieved (a) by connecting the evaluation board with the Micro USB to USB cable to the development computer and starting the CoolTerm serial console with the script from the repository, (b) by resetting the board, stopping the autoboot and entering the U-Boot prompt, (c) by setting the U-Boot environment variables with the correct IP addresses for the NXP LS1012A FRDM Board and the TFTP server and resetting the board again; (d) and, last, by executing the following update commands:

```

# Environment Setup

=> printenv bootdelay

=> setenv ipaddr <board_ip>

=> setenv serverip <server_ip>

=> saveenv

=> reset

. .

# PBL Update

=> tftp 0x80000000 PBL_0x33_0x05_800_250_1000_default.bin;

=> sf probe 0:0; sf erase 0 40000; sf write 0x80000000 0x0

40000;

# U-Boot Update

=> tftp 0x8000000 u-boot.bin;

sf probe 0:0; sf erase 0x100000 80000; sf write 0x8000000

0x100000 80000;

# Linux Kernel Erase

=> sf probe 0:0; sf erase $kernel_start $kernel_size;

```

After the QSPI flash memory is updated, the custom ARMv8-A binaries start execution at exception level 3. However, to be able to deploy the code of this project, the U-Boot environment variables have to be set according to the configuration file in the appendix C.

version: 1.0

## **3 Practical Part**

This chapter describes those aspects of the bachelor thesis that are closely related to the development of the code written in assembly and Ada/SPARK. In the first part, a detailed explanation of the development environment is given, while as the second part is dedicated to the current project and code structure elaborated during this study.

| identifier       | description                      | link             |

|------------------|----------------------------------|------------------|

| Method           | Dual Boot Desktop PC             | -                |

| Operating System | Debian 64-bit 9.2 64-bit         | Debian Download  |

| Native Toolchain | AdaCore GNAT Community Edition   | AdaCore Download |

| Cross Toolchain  | AdaCore GNAT AArch64 Pro Edition | -                |

| IDE              | AdaCore GPS Community Edition    | AdaCore Download |

| Debugger Code    | AdaCore GDB AArch64 Pro Edition  | -                |

| Debugger Probe   | Segger J-Link Edu                | J-Link Probe     |

| Debugger Driver  | Segger J-Link Driver Package     | J-Link Download  |

| Debugger Connect | OpenOCD 0.10.0 (customised)      | OpenOCD          |

## 3.1 Development Environment

Table 3.1: Development Environment Overview

As the development environment has been most important for the success of this bachelor thesis, this whole section is dedicated to its setup. An overview of all the required tools is given in table 3.1. Due to the requirements of the above mentioned software, the environment setup is based on a Debian 9 operating system with a Gnome desktop. However, the installation of the base system will not be discussed further as there are enough installation guides and configuration options to be found in literature and online.

### 3.1.1 Toolchain

To be able to build all the source code developed during this study, a native Ada/SPARK toolchain for the test project and a Ada/SPARK ARMv8-A AArch64 cross toolchain for the main source code are needed. While the native toolchain provided by the AdaCore Community Project is freely available for almost all operating systems <sup>1</sup>, the GNAT Pro AArch64 ELF cross toolchain currently used for the development is

bachelorthesis.pdf

<sup>&</sup>lt;sup>1</sup>cf. https://www.adacore.com/download, December 21, 2018

part of the AdaCore GNAT Pro Edition<sup>2</sup> and therefore a valid license is needed. Owing to the request of the Muen SK developers, i.e. Adrian-Ken Rüegsegger and Reto Bürki, AdaCore provided a free license for this bachelor thesis. The according installation package is provided with the source code, but it is important to note that this toolchain should only be used in the context of this bachelor thesis (i.e. educational use only). The installation of both the native and the cross toolchain can be done without problems on any Linux derivative with the installation script included in the AdaCore packages.

An alternative way to build a GNAT ARMv8 AArch64 toolchain with the open source GCC GNU Compiler Collection and the software tool crosstool-ng can be found in the evaluation case documentation of the Student Research Study <sup>3</sup>, although this option could not be tested for the current source code during this bachelor thesis.

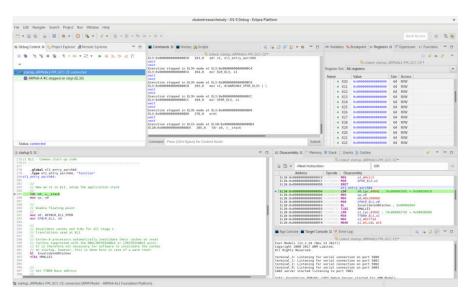

### 3.1.2 Integrated Development Environment

Due to the integration possibilities for the GNAT toolchain, the OpenOCD client and the GNU Debugger (GDB) software, the GPS Integrated Development Environment (IDE) developed by AdaCore was used during the entire project. The IDE is part of the AdaCore toolchain packages and is automatically installed during the AdaCore toolchain installation process.

Apart from the standard tools offered by a full-featured IDE, the GPS IDE also provides a test suite for native unit tests. This suite is used by the Muen SK test project that can be found in the root directory of the code repository.

| File Edit Navigate Find Code VCS Build An | abra Debua SRABK Viau Window Help                 |                |

|-------------------------------------------|---------------------------------------------------|----------------|

|                                           | A P. R. S. R. F. R.                               | Default search |

|                                           |                                                   | Denade, search |

|                                           | 24 11                                             |                |

| <pre>UP The Burnesk</pre>                 | <pre>25  @project NueeDoABM</pre>                 |                |

|                                           | Main                                              | 38:1 🖌 🖷 🕯     |

|                                           | Messages Locations Breakpoints Debugger Variables |                |

|                                           |                                                   |                |

|                                           |                                                   |                |

#### Figure 3.1: GPS IDE overview

<sup>&</sup>lt;sup>2</sup>cf. https://www.adacore.com/gnatpro/, December 21, 2018

<sup>&</sup>lt;sup>3</sup> Problem Description Toolchain - Ada toolchain ARMv8 AArch64, chapter 2, page 3 ff.

### 3.1.3 Debugger Setup

Even though the development of bare metal software does not necessarily require a hardware debugger <sup>45</sup>, the usage of the J-Link Debug Probe in connection with the GNU Debugger and OpenOCD has been of key importance to accomplish the objectives within the time constraints of this bachelor thesis. However, the main problem in this context is that there are hardly any open source or free software products that support the latest ARMv8-A architecture. Therefore, a working combination of hardware and software tools had to be assembled that could provide the desired debugger functionality with as few adjustments as possible.

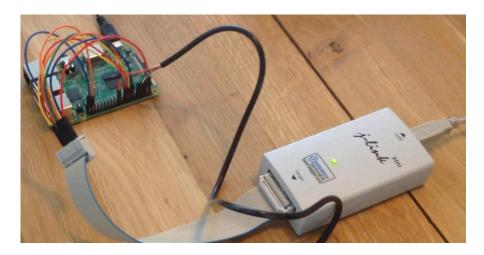

#### J-Link Debug Probe

For this project, the Segger's J-Link Edu Version 10.1 <sup>6</sup> debug probe was chosen as the in-circuit debugger after a thorough examination of various devices and possibilities during the Student Research Study<sup>7</sup>, even though the J-Link software provided with this device does not support the ARMv8-A Cortex-A53 processor yet <sup>8</sup>. The debug probe is used to connect the JTAG header on the NXP LS1012A board to the developer's desktop computer.

Although, this setup uses the OpenOCD software to guarantee a working communication between the J-Link Edu debug probe and the GDB server provided with the GPS IDE, the official drivers from the Segger download page may have to be installed too, depending on the operating system of the development setup. The J-Link Software bundle as well as the documentation can be downloaded from here. As an example, the installation commands for the Debian 9 distribution would be:

\$ cd /path/to/JLink\_Linux\_V640\_x86\_64.deb

\$ su

# enter your root password

\$ dpkg -i JLink\_Linux\_V640\_x86\_64.deb

# and follow the installation instructions

Finally, the NXP LS1012A FRDM Board has to be wired correctly to the Segger J-Link Edu debug probe. Because the NXP evaluation board implements the official JTAG 10-pin interface specified by ARM Limited, the according pinout description can be found in the CoreSight Components Technical

<sup>&</sup>lt;sup>4</sup>Alternatives to a hardware debugger would be an according configured UART communication or a simulator, although every consulted literature, that covers this topic, recommends using a hardware debugger especially when writing boot code (cf. chapter 9, page 159 ff., [3]

<sup>&</sup>lt;sup>5</sup>[4] Loosli. *Student Research Study, Muen on ARM - an Evaluation.* 2017, chapter 3, section 3.1, page 30 ff.

<sup>&</sup>lt;sup>6</sup>https://www.segger.com/products/debug-probes/j-link/models/j-link-edu/, December 21, 2018

<sup>&</sup>lt;sup>7</sup>[4] Loosli. Student Research Study, Muen on ARM - an Evaluation. 2017, chapter 3, section 3.1.2, page 31 f.

<sup>&</sup>lt;sup>8</sup>At the end of the second quarter of 2018, Segger released a beta version of the J-Link software package with ARMv8-A support (cf. https://www.segger.com/news/j-link-64-bit-support, December 21, 2018). However, this package is currently only supported by the J-Link Ultra+ debug probe (cf. https://forum.segger.com/.../5234-SOLVED-armv8-iMX8M-Support and https://www.segger.com/.../model-overview, December 21, 2018).

Bachelor Thesis Muen on ARM

Reference Manual<sup>9</sup>. The pinout description for the Segger J-Link Edu debug probe is explained in the Segger J-Link documentation<sup>10</sup>. The final setup is shown in figure 3.2.

Figure 3.2: J-Link Debug Probe setup including ARM JTAG pinout

#### OpenOCD

For the communication between the J-Link debug probe and the GDB server, the Open On-Chip Debugger (OpenOCD) software created by Dominic Rath as part of a diploma thesis at the University of Applied Sciences Augsburg was chosen <sup>11</sup>. As the ARMv8-A support is still under development, the latest source code from the master branch of the sourceforge repository <sup>12</sup> has to be adapted with two patches provided with the source code for this bachelor thesis <sup>13</sup>. After applying the patches to the downloaded source code of the OpenOCD software, the project has to be built and installed according to the instructions that can be found in the root directory of the OpenOCD master branch.