OS for Use in the Operating Systems

Print time:

11.06.2025

Team / Authors:

Matteo Gmür and Fabian Imhof

Advisors:

Felix Morgner

Copy editor:

**Thomas Letsch**

# **Abstract**

TeachOS is an operating System for the x86\_64 CPU architecture. It is designed to be an interactive learning tool used in the «Operating Systems 1» and «Operating Systems 2» lecture track at OST.

As part of a previous thesis, a foundation in form of memory management, including physical and heap memory was created. Topics covered included parsing Multiboot2 information, implementing frame allocation and page tables, and using these components to remap the kernel. Based on this, dynamic memory allocation during kernel runtime was implemented using different allocation strategies.

This paper examines the core concept of context-switching in operating systems for the x86 processor architecture. To implement the context-switch mechanisms, multiple operating system concepts had to be researched and implemented. These concepts include Privilege Levels, the Global Descriptor Table, Interrupts and the Interrupt Descriptor Table and Procedure Calls.

To give the newly created access to user mode a purpose, the existing heap implementation has been expanded upon, by utilizing the new and delete operators in various data-structures. Additionally a separate user mode heap has been created, which is separated from the kernel mode heap via paging, and is dynamically extended when running out of memory.

This foundation can be extended in the future, by separating kernel-code and user-code binaries. Doing this allows for better separation of the different privilege levels inside the paging mechanism, which in turn better resembles real world operating systems, and thus better fulfills the primary goal of providing an operating system designed for education.

i

# **Table of Contents**

| T | Goa  | IIS                                                     | ⊥  |

|---|------|---------------------------------------------------------|----|

|   | 1.1  | Scope                                                   | 1  |

|   |      | Memory Management                                       |    |

|   |      | Context Switching                                       |    |

|   |      |                                                         |    |

|   | 1.4  | Out of scope                                            | 1  |

| 2 | Rese | earch                                                   | 3  |

|   |      | User Mode Heap                                          |    |

|   | 2.1  | 2.1.1 Decision                                          |    |

|   | 2 2  |                                                         |    |

|   |      | Privilege levels                                        |    |

|   |      | Interrupts                                              |    |

|   | 2.4  | Global Descriptor Table                                 |    |

|   |      | 2.4.1 Segment Descriptor                                | 6  |

|   |      | 2.4.2 Segment Selector                                  | 10 |

|   |      | 2.4.3 Descriptor Table Pointer                          | 10 |

|   |      | 2.4.4 Segment Registers                                 |    |

|   |      | 2.4.5 Far Pointer                                       |    |

|   | 2 5  | Interrupt Descriptor Table                              |    |

|   | 2.5  | 2.5.1 Gate Descriptors                                  |    |

|   | 2.0  | ·                                                       |    |

|   | 2.6  | Task State Segment                                      |    |

|   |      | 2.6.1 Memory Management Register                        |    |

|   | 2.7  | Procedure Calls                                         |    |

|   |      | 2.7.1 SYSCALL / SYSRET                                  | 17 |

|   |      | 2.7.2 SYSENTER / SYSEXIT                                | 18 |

|   |      | 2.7.3 INT/IRETQ                                         |    |

|   |      | 2.7.4 Decision                                          |    |

|   |      | 2.7.5 Passing Arguments to System Calls                 |    |

|   |      | 2.7.6 Decision                                          |    |

|   |      |                                                         |    |

|   |      | 2.7.7 Using System Calls with multiple stacks           | 21 |

| 3 | Resi | ults                                                    | 22 |

|   |      | Memory Management                                       |    |

|   | 0    | 3.1.1 Current problem                                   |    |

|   |      | 3.1.2 Overriding new and delete                         |    |

|   |      | · · · · · · · · · · · · · · · · · · ·                   |    |

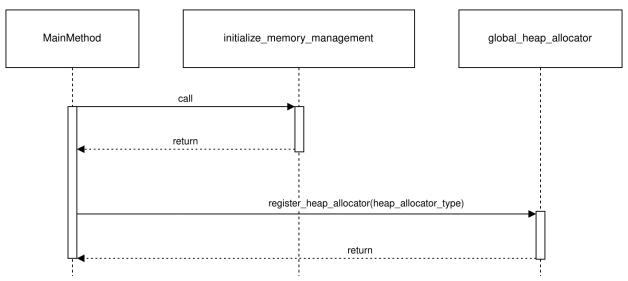

|   |      | 3.1.3 Global Heap Allocator                             |    |

|   |      | 3.1.4 Factory Method Pattern                            |    |

|   |      | 3.1.5 Improving the Linked List Allocator               |    |

|   | 3.2  | Context Switching                                       |    |

|   |      | 3.2.1 Segment Descriptor                                | 25 |

|   |      | 3.2.2 Global Descriptor Table                           | 27 |

|   |      | 3.2.3 Interrupt Descriptor Table (IDT)                  | 28 |

|   |      | 3.2.4 Interrupt Service Routine (ISR)                   |    |

|   |      | 3.2.5 Task State Segment (TSS)                          |    |

|   |      | 3.2.6 Changing Segment Registers                        |    |

|   | 2 2  |                                                         |    |

|   | 5.5  | Separating User from Kernel Mode                        |    |

|   |      | 3.3.1 Configuring and Enabling System Calls             |    |

|   |      | 3.3.2 Implementing and Wrapping System Calls            |    |

|   |      | 3.3.3 Implementing the System Call Handler              |    |

|   |      | 3.3.4 Creating and Moving Code into User Linker Section | 35 |

|   |      | 3.3.5 Mapping Pages User Accessible                     | 35 |

|   |      | 3.3.6 Creating a User Heap Allocator                    | 37 |

| , |      | •                                                       |    |

| 4 |      | embly caveats                                           |    |

|   |      | GNU Assembly (GAS)                                      |    |

|   | 4.2  | Inline assembly                                         | 39 |

|   |      | 4.2.1 Output operands                                   | 39 |

|   |      | 4.2.2 Input operands                                    | 39 |

|   |      | 4.2.3 Clobber list                                      |    |

|   |      | 4.2.4 Operand constraints                               |    |

|   |      | 4.2.5 Constraint modifiers                              |    |

|   |      | 4.2.6 Compile time optimization                         |    |

|   |      |                                                         |    |

|   |      | 4.2.7 Loading effective address                         | 40 |

| 5 | Future Work                       | 41 |

|---|-----------------------------------|----|

|   | 5.1 Interrupt Handler             | 41 |

|   | 5.2 System Call over Interrupts   | 41 |

|   | 5.3 Interrupt Stack               | 41 |

|   | 5.4 System Call Parameter Passing | 41 |

|   | 5.4 System Call Parameter Passing | 41 |

|   | 5.6 Creating a User Mode Stack    | 41 |

|   | 5.6 Creating a User Mode Stack    | 41 |

| 6 | Glossary                          |    |

| 7 | Bibliography                      | 45 |

| 8 | Table of Figures                  | 4  |

| • | 8.1 Listings                      | 45 |

|   | 8.2 Images                        | 46 |

|   | 8.2 Images                        | 46 |

|   | 8.4 Tools                         |    |

# Part 1 Goals

# 1.1 Scope

This project focuses on enhancing the TeachOS operating system with improved memory management, task creation, and user- and kernel-space interaction. The main areas of development include:

- · Context switching

- ► Implement interrupt handling

- ▶ Enable paging in user space

- Create user-mode heap

- Ensure correct permissions for the different modes

- Custom Memory Management and Data Structures

- Override new and delete to use a heap allocator based on current protection level

- ▶ Build reusable infrastructure to replace parts of the C++ standard library (e.g. std::vector, std::unique pointer)

# 1.2 Memory Management

The memory management should be improved, by making heap allocation as simple as possible. This is required for efficient and viable memory management inside all privilege levels. These improvements have the highest priority and should be implemented first.

The current memory management implementation contains various deficiencies that require some tweaking to be more optimal and developer-friendly:

- Connect memory management infrastructure to new and delete calls

- Create custom implementations of C++ Standard Library constructs like std::vector which use the custom memory management infrastructure

- Improve linked\_list\_allocator to allow for delete calls without passing a size attribute (Storing the size in a header of the allocated block instead)

# 1.3 Context Switching

The primary goal of this bachelor thesis is implementing the ability to switch between privilege levels. Meaning it should be possible to execute code in user mode and switch to kernel mode via syscall to handle more privileged instructions.

This goal essentially consists of the following tasks:

- Creating a global descriptor table with kernel and user segment descriptors

- · Creating an interrupt descriptor table to avoid system crashes due to exceptions

- Mapping kernel code and user code onto different pages

- Updating the (permission) flags of all page tables to correctly represent their purpose

- Switching into user-mode at the end of kernel initialization so that the "default" operating mode is in privilege level 3

- Setting up the system in a way, that allows syscalls inside user mode, to allow switching the current privilege level to let the kernel handle calls requiring elevated privileges

# 1.4 Out of scope

Currently TeachOS is turning out to be an operating system kernel running on a single processing core. Partly because of the limited resources available during the bachelor thesis. For this reason a multithreaded implementation of any functionality is out of scope. This results in syscalls invoked in user mode being blocking until the kernel is done handling it.

The creation of code solely for educational purposes will also be disregarded in this thesis. One reason is that the kernel is not yet in a state, in which it could immediately be used in a classroom. All the in-scope work is necessary for these features to be effective. This will be explained further in Section 5, "Future work".

Another interesting and worthwhile feature is implementing appropriate keyboard input handling. However, a complete interrupt handling would have to be implemented first, which is simply not possible due to the time constraint of this thesis. For this reason, keyboard interrupt handling is also mentioned as a possible feature to implement next in Section 5, "Future work".

# Part 2 Research

# 2.1 User Mode Heap

There are three different ways to implement a separate heap for User Mode. This is done to ensure that user applications can not interfere with the kernels' memory management.

All strategies share that they require an additional heap area to be mapped, so instead of only having a 100 KiB Kernel Heap, they also require a separately mapped Heap for User Mode.

| Strategy                                                                                        | Advantages / Disadvantages                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Changing allo-<br>cation calls de-<br>pending on CS<br>register                                 | Advantages:  • Allows to keep the current operator overloads for Kernel and User Mode  • Check the value of the CS register, when the new or delete operator is called  • Depending on the value, either allocate memory in User Mode Heap or Kernel Mode Heap  • Implementation is relatively simple, because it allows to keep the current infrastructure and requires to simply add another member variable to the global_heap_allocator |

|                                                                                                 | Disadvantages:  Kernel and User Mode Heap Allocation are not cleanly separated and can not be separated later without a rewrite                                                                                                                                                                                                                                                                                                             |

| Use template<br>argument for<br>allocator with<br>separate Kernel<br>and User Mode<br>Allocator | Advantages:  Uses an additional template argument to pass a custom allocator, depending on the mode for Standard Template Library (STL) implementations  Kernel can use kmalloc / kfree and User Mode can use malloc / free which forward to SYSCALL  User Mode can be the default Allocator used                                                                                                                                           |

|                                                                                                 | Disadvantages: Requires more work, because separate allocators need to be written that forward calls to SYSCALL                                                                                                                                                                                                                                                                                                                             |

| Place User<br>Mode operator<br>overload in sep-<br>arate linker sec-<br>tion, loaded in         | Advantages:  Cleanest way, allows to simply implement another set of new and delete operator overloads  Use separate page tables to only load ELF section in User Mode where the User Mode implementation is contained and not the Kernel Mode implementation                                                                                                                                                                               |

| Ring 3                                                                                          | <ul> <li>Disadvantages:</li> <li>Hard to explain, Linker does Magic in the background. Suboptimal for teaching functionality of the operating system</li> <li>Hard to put the implementation into the correct Linker section</li> <li>Would require splitting the binary, because the new and delete can not be redefined</li> </ul>                                                                                                        |

Table. 1: Comparison of User Mode Heap Implementations

#### 2.1.1 Decision

With these three options available, a decision must be made as to which of them TeachOS should utilize.

Option 3 currently can not be implemented, because it would require splitting User and Kernel Code into different binaries.

Option 2 is a viable option, but it only allows using STL data structures in user mode. However, it does not enable using new or delete calls directly to instantiate an arbitrary data structure. Therefore, the best option for this operating system is Option 1 combined with Option 2, which has been chosen.

This decision is motivated by the following factors:

- Extensibility: The decision tree inside the new / delete operators have been modified to additionally use Option 2, because the actual allocation calls kmalloc / malloc and deallocation calls kfree / free have been separated into a user and kernel method already. Which then individually call their respective Allocator implementation.

- Learning value: The code is relatively simple and therefore makes understanding, what exactly happens clearer and more useful as a learning tool.

# 2.2 Privilege levels

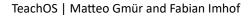

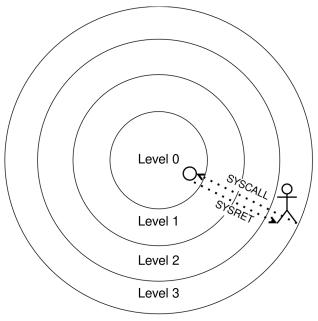

Privilege levels are a protection mechanism. There are four protection levels (0 to 3) with level 0 being the most privileged and decreasing with every higher level. Privilege levels are used to prevent a program operating at a lesser privilege level from accessing a segment with a greater privilege level. Instead, this attempted access will generate a General Protection Fault (#GP).

Image. 1: Operating system protection ring (Figure 6-3. Protection Rings [1])

There are multiple recognized types of privilege levels, that check access between Code and Data Segments.

| Name                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current Privilege Level (CPL)    | Stored in bits 0-1 of the CS and SS registers. Equivalent to the privilege level of the Code Segment the current instructions are being fetched from, for nonconforming Code Segments. Changed when control is being transferred to a Code Segment with a different privilege level, besides for conforming Code Segments, here the CPL is not changed even if control is transferred.                                                                                                           |

| Descriptor Privilege Level (DPL) | Describes privilege level of Segment Descriptor (Section 2.4.1) or Gate Descriptor (Section 2.5.1). Interpretation depends on the type of segment or gate:  • Data Segment / TSS / Call Gate: Indicates the numerically highest CPL that is allowed to access the segment.  • Nonconforming Code Segment: Exact CPL required to access the segment.  • Conforming Code Segment (or Nonconforming through Call Gate): Indicates the numerically lowest CPL that is allowed to access the segment. |

| Requested Privilege Level (RPL)  | Overrides the value of the CPL. Uses either the CPL or RPL value for actual privilege level checks, depending on which value is numerically higher.                                                                                                                                                                                                                                                                                                                                              |

Table. 2: Types of Privilege Levels (Vol. 3A, Chapter 6.5 Privilege Levels [1])

# 2.3 Interrupts

Interrupts are signals generated by devices, such as keyboards or hard drives, or code, that instruct the CPU to halt its current operations and address a different task. For instance, when a key is pressed on a keyboard, the keyboard controller sends an interrupt to the CPU. This allows the operating system to promptly display the corresponding character on the screen, regardless of the CPU's previous activity, after which the CPU can resume its prior task.

When receiving a specific interrupt, the CPU consults a designated table provided by the operating system to locate the relevant entry for that interrupt. In the x86\_64 architecture, this table is referred to as the Interrupt Descriptor Table (IDT). Once the CPU identifies the appropriate entry for the interrupt, it executes the code associated with that entry. This code is called "interrupt service routine" (ISR) or "interrupt handler".

There are usually three different types of interrupts: Exceptions, Interrupt requests / Hardware interrupts and Software interrupts. (Article "Interrupts" [2])

# 2.4 Global Descriptor Table

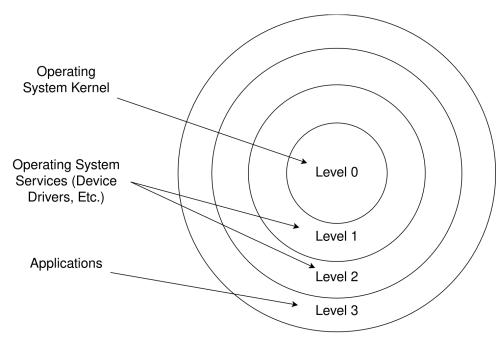

The Global Descriptor Table (GDT) is a fundamental component of memory management in the x86 architecture. In 32-bit mode it is used as a data structure by the CPU to define and separate memory segments in a system.

In IA-32e 64-bit mode, segmentation using the GDT has been replaced with paging, which is instead used to separate memory into protected areas. This causes the CPU to simply treat all Base field values as if they were 0, regardless of the actual value in the Segment Descriptor. Additionally, limit checks for the registers are disabled and the values of the Limit field are ignored as well. (Vol. 3A, Chapter 3.2.4 Segmentation in IA-32e Mode [1])

Therefore, the setup of the GDT can be minimal in IA-32e 64-bit mode, as it is only used for Context Switching. This minimal setup requires an empty "Null Descriptor" at the start, followed by a Code Segment Descriptor and a Data Segment Descriptor for Kernel Mode, a Code Segment Descriptor and Data Segment Descriptor for User Mode and lastly a Task State Segment Descriptor.

Image. 2: GDT segments in IA-32e 64-bit mode

During the setup of the GDT it is important to ensure that no interrupts are occurring. The code initializing the GDT must not get interrupted, because the program could still attempt to access the segment registers of the old GDT structure. [3]

To prevent this, all interrupts have to be temporarily disabled. This can be achieved by clearing the interrupt flag using the cli instruction. Once the IDT has been set up interrupts can again be enabled, simply by setting the interrupt flag again through the sti instruction. This will additionally cause any hardware interrupts that were ignored while the flag was cleared, to be received again as soon as the flag has been set.

# 2.4.1 Segment Descriptor

The memory segments inside the GDT are called Segment Descriptors and contain the following data for the 64-bit version.

| 127 |          |    |     |     |     |     |     |           |    |      | 96 |  |  |

|-----|----------|----|-----|-----|-----|-----|-----|-----------|----|------|----|--|--|

|     | Reserved |    |     |     |     |     |     |           |    |      |    |  |  |

| 95  |          |    |     |     |     |     |     |           |    |      |    |  |  |

|     | Base     |    |     |     |     |     |     |           |    |      |    |  |  |

| 63  |          |    |     |     |     |     |     |           |    |      | 32 |  |  |

| 63  |          | 56 | 55  | 52  | 51  | 48  | 47  | 40        | 39 |      | 32 |  |  |

|     | Base     |    | Fla | ıgs | Lir | nit | Acc | cess Byte |    | Base |    |  |  |

| 31  |          | 24 | 3   | 0   | 19  | 16  | 7   | 0         | 23 |      | 16 |  |  |

| 31  |          |    |     |     |     | 16  | 15  |           |    |      | 0  |  |  |

|     |          | Ва | se  |     |     |     | L   | mit       |    |      |    |  |  |

| 15  |          |    |     |     |     | 0   | 15  |           |    |      | 0  |  |  |

Image. 3: 64-bit Segment Descriptor [1] (Figure 3-8. Segment Descriptor)

The Base and Limit fields are divided across multiple separate fields. While this might initially seem unusual, it originated for historical reasons to maintain backwards compatibility with the 16-bit processor format of the 80286 and the 32-bit processor format of the 80368 processor. The 16-bit processor does not require the additional Flags field, because it is primarily used to signal 32-bit instead of 16-bit registers. Furthermore, it also does not require the 4 additional bits for the Limit field or the additional 8 bit for the Base field. Instead, these 16 bit have to be 0 and reserved to keep compatibility between both processor formats.

| 63 |          | 48 | 47     | 40    | 39 |      | 32 | 63 |      | 56  | 55  | 52  | 51 48 | 47   | 40       | 39 |      | 32 |

|----|----------|----|--------|-------|----|------|----|----|------|-----|-----|-----|-------|------|----------|----|------|----|

|    | Reserved |    | Access | Byte  |    | Base |    |    | Base |     | Fla | ags | Limit | Acce | ess Byte |    | Base |    |

|    |          |    | 7      | 0     | 23 |      | 16 | 31 |      | 24  | 3   | 0   | 19 16 | 7    | 0        | 23 |      | 16 |

| 31 |          | 16 | 15     |       |    |      | 0  | 31 |      |     |     |     | 16    | 15   |          |    |      | 0  |

|    | Base     |    |        | Limit |    |      |    |    | Ва   | ıse |     |     |       | Lir  | nit      |    |      |    |

| 15 |          | 0  | 15     |       |    |      | 0  | 15 |      |     |     |     | 0     | 15   |          |    |      | 0  |

**Table. 3:** 16-bit Segment Descriptor (Figure 6-1. Protection Fields of Segment Descriptors [4]) and 32-bit Segment Descriptor (Figure 6-3. Segment Descriptors [5])

| Bits | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32   | Reserved    | Required because the 64-bit version of the Segment Descriptor requires a 64-bit base address instead of only a 32-bit address. This means our new entry would be 96 bit (64 bit from 32-bit Segment Descriptor + 32 bit for remaining half of the base address). However, to be compatible with the design of the 32-bit Segment Descriptor, two entries in little-endian format are now needed in the Global Descriptor Table, because those two entries would add up to 128-bit, the remaining space has to be filled with reserved data. |

| 64   | Base        | Defines the starting memory address of the segment within the 4-GiB linear address space. Is calculated by combining the three base address fields to form a single 64-bit value.                                                                                                                                                                                                                                                                                                                                                           |

| 4    | Flags       | Defines 4 individual bits that change the behavior of the Segment Descriptor.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 20   | Limit       | Defines the size of the segment. Is calculated by combining the two limit fields to form a single 20-bit value. Behavior depends on the Granularity flag in the Flags field.  • 0: Segment size ranges from 1 Byte to 1 MiB, in byte increments  • 1: Segment size ranges from 4 KiB to 4 GiB in 4 KiB increments                                                                                                                                                                                                                           |

| 8    | Access Byte | Defines 8 individual bits that change the type of the Segment Descriptor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table. 4: Segment Descriptor Components (Vol. 3A, Chapter 3.4.5 Segment Descriptors [1])

# 2.4.1.1 Flags

IA-32e mode can run in 64-bit mode or 32-bit compatibility mode. However, because Long Mode is enabled, IA-32e in 64-bit mode is used and therefore bit 2 is always enabled for Code Segments.

Flags: Data-Segment Descriptor Flags: Code-Segment Descriptor

| Granularity | Big | 0 | Available | Granularity | Default | Length | Available |

|-------------|-----|---|-----------|-------------|---------|--------|-----------|

|-------------|-----|---|-----------|-------------|---------|--------|-----------|

Flags: System-Segment Descriptor

| Granularity | 0 | 0 | 0 |

|-------------|---|---|---|

|             |   |   |   |

Table. 5: Differences in Flags on different Segment Descriptor Types (Vol. 3A, Chapter 3.4.5 Segment Descriptors [1])

| Bit | Name          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Available     | Segment is available for use by the system software                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2   | Length        | Defines the size of the Code Segment descriptor. Should be 0 for non Code Segment Descriptors. If this bit is set, the third bit should always be 0. Only defined for IA-32e mode, for other modes this bit should be 0.  • 0: Defines a 32-bit Compatibility Code Segment  • 1: Defines a 64-bit Code Segment                                                                                                                                                                                                             |

| 3   | Default / Big | Behavior depends on the actual type of the segment descriptor.  Code Segment: Flag indicates the default length for effective addresses and operands  O: 16-bit addresses and 16-bit or 8-bit operands  Stack Segment: Specifies the size of the Stack Pointer (SP) used for implicit stack operations  O: 16-bit SP stored in 16-bit Extended Stack Pointer (ESP) register (value 0)  1: 32-bit SP stored in 32-bit ESP register  Expand-Down Data Segment: Specifies the upper bound of the segment  O: 64 KiB  1: 4 GiB |

| 4   | Granularity   | Signifies the resolution of the Limit value.  • 0: Scaled by 1 Byte  • 1: Scaled by 4 KiB blocks                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table. 6: Segment Descriptor Flags (Little-Endian) (Vol. 3A, Chapter 3.4.5 Segment Descriptors [1])

# 2.4.1.2 Access Byte

| Bit | Name                          | Description                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-4 | Type Field                    | Further specifies the underlying type of the segment, depends on the Descriptor Type.                                                                                                                                                                                                                                                                                                                       |

| 5   | Descriptor Type               | Defines the underlying type of the segment.  • 0: System Segment  • 1: Code or Data Segment                                                                                                                                                                                                                                                                                                                 |

| 6-7 | Descriptor Privilege<br>Level | Specifies the privilege level required to access this segment. A higher value means a less privileged access level is required. If only two access levels are required it is recommended to use the highest (0) and the lowest access level (3) respectively.  • 0: Level 0 (Kernel)  • 1: Level 1 (Used for System Services like Device Drivers)  • 2: Level 2  • 3: Level 3 (User Applications)           |

| 8   | Segment-present               | Indicates whether the segment is present in memory or not. Will cause a Segment Not Present (#NP) exception, when this Segment Descriptor is loaded while the value is 0.  Allows for more fine-grained control of segments that are actually loaded into physical memory at a give time. (Vol. 3A, Chapter Interrupt 11—Segment Not Present (#NP) [1])  • 0: Not present in memory  • 1: Present in memory |

Table. 7: Segment Descriptor Access Byte (Little-Endian) (Vol. 3A, Chapter 3.4.5 Segment Descriptors [1])

# 2.4.1.3 Type Field

| Descriptor<br>Type | Т   | ype: Data-Seg          | ment Descript | or       | Descriptor<br>Type | Ту | /pe: Code-Seg | ment Descript | or       |

|--------------------|-----|------------------------|---------------|----------|--------------------|----|---------------|---------------|----------|

| 1                  | 0   | Expansion<br>Direction | Writable      | Accessed | 1                  | 1  | Conforming    | Readable      | Accessed |

| Descriptor<br>Type | Тур | oe: System-Se          | gment Descrip | otor     |                    |    |               |               |          |

| 0                  |     | Ту                     | ре            |          |                    |    |               |               |          |

Table. 8: Differences in Type Field on different Segment Descriptor Types (Figure 6-1. Descriptor Fields Used for Protection [1])

#### 2.4.1.3.1 Type Field for Data or Code Segments Descriptors

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Behavior is the same for both types Code and Data Segment Descriptors. Whether the segment has been accessed since the last time the operating system has cleared the flag or not.  • 0: Not accessed  • 1: Accessed                                                                                                                                                                                                                                                                                 |

| 2   | Behavior depends on the specific type of the Segment Descriptor as indicated by bit 0.  • Data Segment: Determines if the segment is writable or only readable  • 0: Read-Only  • 1: Read-Write  • Code Segment: Indicates if the segment can be read or only executed  • 0: Execute-Only  • 1: Execute-Read                                                                                                                                                                                         |

| 3   | Behavior depends on the actual type of the Segment Descriptor possible in bit 0.  • Data Segment: Whether the segment expands downwards or upwards  • 0: Expand-Up  • 1: Expand-Down  • Code Segment: Whether the code is allowed to be executed by different access levels (higher or lower)  • 0: Nonconforming (Access by different access level causes a General Protection Fault (#GP) exception, Data Segments are always nonconforming, but allow access from higher levels)  • 1: Conforming |

| 4   | Defines the actual type of the segment.  • 0: Data Segment  • 1: Code Segment                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table. 9: Segment Descriptor Type Field (Little-Endian) (Vol. 3A, Chapter 3.4.5 Segment Descriptors [1])

#### 2.4.1.3.2 Type Field for System Segment Descriptors

The Type field for System Segment Descriptors is a special case. This is because the individual bits are not standalone flags. Rather, specific combinations of bits are used to identify the exact type of system segment. Since IA-32e 64-bit mode is in use, only the 64-bit versions of these types are applicable.

All other possible values (0-15) not mentioned below, are reserved for backwards compatibility with 32-bit addresses.

| Decimal | Bits          | IA-32e Mode                               |  |  |  |

|---------|---------------|-------------------------------------------|--|--|--|

| 2       | 0   0   1   0 | Local Descriptor Table (LDT)              |  |  |  |

| 9       | 1   0   0   1 | 64-bit Task State Segment (TSS) Available |  |  |  |

| 11      | 1   0   1   1 | 64-bit Task State Segment (TSS) Busy      |  |  |  |

| 12      | 1   1   0   0 | 64-bit Call Gate                          |  |  |  |

| 14      | 1   1   1   0 | 64-bit Interrupt Gate                     |  |  |  |

| 15      | 1   1   1   1 | 64-bit Trap Gate                          |  |  |  |

Table. 10: System Segment Descriptor Type Field (Table 3-2. System-Segment and Gate-Descriptor Types [1])

#### 2.4.1.4 Segment Types

The Segment Descriptors point to actual Segments, which have different uses depending on their specific type.

- Code Segment: Stores executable instructions

- Data Segment: Stores variables and data

- ► Expand-Down Data Segment: Arbitrary Data Segment that expands downwards

- Stack Segment: Special Data Segment that is pointed to by the Stack-Segment (SS) register. Defines the block of memory that will be used to save stack information. Can also be an Expand-Down Data Segment (Default / Big flag will be used to signify both settings). Additionally has to allow for both Read / Write, or it will cause a GP exception to be thrown.

- System Segments: Includes TSS and LDT

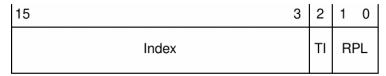

# 2.4.2 Segment Selector

The Segment Selector is a special pointer that identifies a segment in memory through descriptors in the GDT. It allows selecting any of the preconfigured entries, however selecting the first entry of the GDT (Null Segment Descriptor), will not directly generate an exception. But, if the CS or SS registers are accessed when they have a Segment Selector pointing to that entry as the value, it will cause a General Protection Fault (#GP) to be thrown.

Image. 4: 16-bit Segment Selector (Figure 3-6. Segment Selector [1])

| Bit  | Name                           | Description                                                                                                                                                                                                                      |

|------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-1  | Requested Privi-<br>lege Level | See RPL in Section 2.2                                                                                                                                                                                                           |

| 2    | Table Indicator                | Specifies Descriptor Table to be used:  • 0: Selects the GDT  • 1: Selects the current LDT                                                                                                                                       |

| 3-15 | Index                          | Select one of the possible $2^{12}=8192$ descriptors in the GDT or LDT. Processor simply multiplies value by 8 (size of the Segment Selector in bytes in 32-bit mode) and adds the result to the base address of the GDT or LDT. |

Table. 11: Segment Selector Components (Vol. 3A, Chapter 3.4.2 Segment Selectors [1])

# 2.4.3 Descriptor Table Pointer

The descriptor table pointer defines an 80-bit structure in IA-32e 64-bit mode, used by both the IDTR and GDTR registers to allow the CPU access to the IDT and GDT respectively.

| 79 |                     | 16 | 15    | 0     |

|----|---------------------|----|-------|-------|

|    | Linear Base Address |    | Table | Limit |

Image. 5: 80-bit Descriptor Table Pointer (Vol. 3A, Chapter 2.4 Memory-Management Registers [1])

| Bits | Name                | Description                                                    |

|------|---------------------|----------------------------------------------------------------|

| 16   | Table Limit         | Defines the amount of bytes in the Descriptor Table.           |

| 64   | Linear Base Address | Defines the address of the first byte in the Descriptor Table. |

Table. 12: Descriptor Table Pointer Components (Vol. 3A, Chapter 2.4 Memory-Management Registers [1])

# 2.4.4 Segment Registers

A segment register allows accessing a particular segment in memory. This is achieved using a Segment Selector to the Segment Descriptor in the GDT and then accessing the register, which will access the segment in memory.

| Register | Full Name                         | Description                                                                                                                                                                                                                                                    |

|----------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS       | Code Segment Register             | Contains Segment Selector to the Code Segment, where the currently executing instructions are stored. Cannot be loaded explicitly and is instead loaded implicitly through instructions or internal processor operations that pass control to another segment. |

| SS       | Stack Segment Register            | Contains Segment Selector to a Stack Segment. In IA-32e 64-bit mode it can simply be the Data Segment as well.                                                                                                                                                 |

| DS       | Data Segment Register             | Contains Segment Selector to a Data Segment.                                                                                                                                                                                                                   |

| ES       | Extra Segment Register            | Contains Segment Selector to a Data Segment.                                                                                                                                                                                                                   |

| FS / GS  | General Purpose Segment Registers | Contains Segment Selector to a Data Segment.                                                                                                                                                                                                                   |

Table. 13: Segment Registers (Vol. 1, 3.4.2 Segment Registers [1])

#### 2.4.5 Far Pointer

Allows referencing methods from Code Segments in the GDT, other than the currently loaded segment.

| 79 64               | 63 0   |

|---------------------|--------|

| Segment<br>Selector | Offset |

Image. 6: 64-bit Far Pointer (Figure 4-5. Pointers in 64-Bit Mode [1])

| Bits | Name             | Description                                                              |

|------|------------------|--------------------------------------------------------------------------|

| 64   | Offset           | Defines the address to the procedure that should be called or jumped to. |

| 16   | Segment Selector | Selects the destination Code Segment, see Section 2.4.2.                 |

Table. 14: Far Pointer Components (Vol. 3A, Chapter 4.3.1 Pointer Data Types in 64-Bit Mode [1])

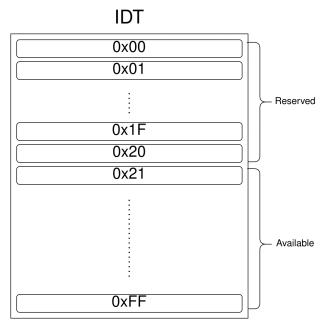

# 2.5 Interrupt Descriptor Table

The Interrupt Descriptor Table (IDT) is a data structure similar to the GDT. Its pointer is loaded into the Interrupt Descriptor Table register (IDTR).

The IDT can hold up to 256 entries, of which the first 22 have a predefined purpose defined by the x86 architecture, and an additional 10 are reserved for future use. The 224 remaining entries however, can be used as needed.

Image. 7: IDT items in x86 (Table 6-1. Exceptions and Interrupts [1])

Each interrupt type is assigned a unique ID, which the processor uses as the index of the IDT. This IDT entry then points to a specific interrupt handler. When an interrupt occurs, the processor stops executing the current task and transitions to that handler to address it. Once the handler has finished processing the interrupt, control is returned to the program or task that was interrupted.

The following table displays some of the more well known predefined interrupts and exceptions which must be present in form of an entry in the IDT.

| Vector | Description                          | Source                                      |

|--------|--------------------------------------|---------------------------------------------|

| 0      | Divide Error                         | DIV and IDIV instructions.                  |

| 3      | Breakpoint                           | INT3 instruction.                           |

| 10     | Invalid TSS                          | Task switch or TSS access.                  |

| 12     | Stack Segment Fault                  | Stack operations and SS register loads.     |

| 14     | Page Fault                           | Any memory reference.                       |

| 16     | Floating-Point Error<br>(Math fault) | Floating-Point or WAIT / FWAIT instruction. |

**Table. 15:** Exceptions and Interrupts (Table 6-1. Exceptions and Interrupts [1])

When an interrupt happens the type of the interrupt defines how the CPU must continue handling its instructions after the interrupt handler is done. This is defined by the gate type field in the IDT entry of the specific interrupt. In case of an exception, it is important to save the address of the currently executing instruction so that it can be retried. These interrupts are called traps. In case of an interrupt request, the address of the next instruction must be saved to prevent the CPU from repeatedly executing the same instruction.

A third kind of interrupt gate type exists, called the "Task Gate". However, this type is not used in Long Mode and is specifically for hardware task switching, which is why it is not further referenced in this document.

# 2.5.1 Gate Descriptors

Similar to the GDT, the IDT contains multiple entries, which are called Gate Descriptors.

| 127 |                  |      |      |      |     |     |     | 96 |

|-----|------------------|------|------|------|-----|-----|-----|----|

|     |                  | Rese | erve | t    |     |     |     |    |

| 95  |                  |      |      |      |     |     |     | 64 |

| 63  |                  | Off  | set  |      |     |     |     | 32 |

| 63  |                  | 48   | 47   |      | 40  | 39  |     | 32 |

|     | Offset           |      |      | Туре |     |     | IST |    |

| 31  |                  | 16   | 7    |      | 0   | 7   |     | 0  |

| 31  |                  | 16   | 15   |      |     |     |     | 0  |

|     | Segment Selector |      |      |      | Off | set |     |    |

| 15  |                  | 0    | 15   |      |     |     |     | 0  |

Image. 8: 64-bit Gate Descriptor (Figure 7-8. 64-Bit IDT Gate Descriptors [1])

The structure looks similar to a Segment descriptor (Section 2.4.1), this is the case because it also grew historically from a 16-bit and 32-bit variant of the same structure.

| 63 |                  | 48 | 47 |      | 40  | 39  | 32     | 63 |                  | 48 | 47 |      | 40  | 39     | 32 |

|----|------------------|----|----|------|-----|-----|--------|----|------------------|----|----|------|-----|--------|----|

|    | Reserved         |    |    | Туре |     | Res | served |    | Offset           |    |    | Type |     | Reserv | ed |

| 31 |                  | 16 | 7  |      | 0   | 7   | 0      | 31 |                  | 16 | 7  |      | 0   | 7      | 0  |

| 31 |                  | 16 | 15 |      |     |     | 0      | 31 |                  | 16 | 15 |      |     |        | 0  |

|    | Segment Selector |    |    |      | Off | set |        |    | Segment Selector |    |    |      | Off | set    |    |

| 15 |                  | 0  | 15 |      |     |     | 0      | 15 |                  | 0  | 15 |      |     |        | 0  |

**Table. 16:** 16-bit Gate Descriptor (Figure 7-10. Gate Descriptor Format [4]) and 32-bit Gate Descriptor (Figure 9-3. 80306 IDT Gate Descriptors [5])

| Bits | Name                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32   | Reserved                       | Required because the 64-bit version of the Gate Descriptor requires a 64-bit base address instead of only a 32-bit address. This means our new entry would be 96 bit (64 bit from 32-bit Gate Descriptor + 32 bit for remaining half of the base address). However, to be compatible with the design of the 32-bit Gate Descriptor, two entries in little-endian format are now needed in the Interrupt Descriptor Table, because those two entries would add up to 128-bit, the remaining space has to be filled with reserved data. |

| 64   | Offset                         | Defines the address to the procedure handling the interrupt of this specific entry.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8    | Туре                           | Define 8 individual bits that change the behavior of the Gate Descriptor.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4    | Interrupt Stack<br>Table (IST) | Leftmost 3 bits are the index into the seven IST pointers of the TSS. Value 0 means the IST Mechanism is not used, Value 1 means IST1 is used. Only available in IA-32e 64-bit mode. (Vol. 3A, Chapter 7.14.5 Interrupt Stack Table [1])                                                                                                                                                                                                                                                                                              |

| 16   | Segment Selector               | Selects the destination Code Segment, see Section 2.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Table. 17: Gate Descriptor Components (Vol. 3A, Chapter 7.14.1 64-Bit Mode IDT [1])

# 2.5.1.1 Type Field

The Task Gate is a special case, because the 4th bit marks the usage of 32-bit, which is always disabled for a Task Gate. This is because the complete Hardware Task Switching mechanism does not exist on IA-32e 64-bit mode and instead has to be implemented in software. Therefore, the Task Gate can not be used in IA-32e 64-bit mode. (Vol. 3A, Chapter 9.7 Task Management in 64-bit Mode [1])

| Type: Interrupt-Gate<br>Descriptor |     |   |   | Type: Trap-Gate Descriptor |   |   |   | Type: Task-Gate Descriptor |   |   |   |   |   |   |     |   |   |   |   |   |

|------------------------------------|-----|---|---|----------------------------|---|---|---|----------------------------|---|---|---|---|---|---|-----|---|---|---|---|---|

| Р                                  | DPL | 0 | 1 | 1                          | 1 | 0 | Р | DPL                        | 0 | 1 | 1 | 1 | 1 | Р | DPL | 0 | 0 | 1 | 0 | 1 |

Table. 18: Differences in Type Field on different Gate Descriptor Types (Figure 7-2. IDT Gate Descriptors [1])

| Bit | Name                          | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-5 | Type Field                    | Defines the actual type of the Gate. Can only be either 32-bit Interrupt or 32-bit Trap in IA-32e 64-bit mode.                                                                                                                                                                                                                                                                                       |

| 6-7 | Descriptor Privilege<br>Level | Specifies the privilege level required to access this gate. A higher value means a less privileged access level is required. If only two access levels are required it is recommended to use the highest (0) and the lowest access level (3) respectively.  • 0: Level 1 (Kernel)  • 1: Level 1 (Used for System Services like Device Drivers)  • 2: Level 2  • 3: Level 3 (User Applications)       |

| 8   | Gate-present                  | Indicates whether the gate is present in memory or not. Will cause a Segment Not Present (#NP) exception, when this Segment Descriptor is loaded while the value is 0.  Allows for more fine-grained control of segments that are actually loaded into physical memory at a give time. (Vol. 3A, Chapter Interrupt 11—Segment Not Present (#NP) [1])  O: Not present in memory  1: Present in memory |

Table. 19: Gate Descriptor Type Field (Little-Endian) (Vol. 3A, Chapter 7.14.1 64-Bit Mode IDT [1])

# 2.6 Task State Segment

The Task State Segment (TSS) is used for managing task switching and is primarily used for hardware task switching by storing the Segment Selectors and Stack Pointers of each privilege level. However, this only applies in Protected Mode. In Long Mode the task switching mechanism of the TSS is not supported. Regardless, the TSS in Long Mode must still exist, because it has been repurposed to hold information that is not directly related to the task-switch mechanism instead. (Vol. 3A, Chapter 9.7 Task Management in 64-bit Mode [1])

| 31 |                      | 15           | 0 |     |  |  |

|----|----------------------|--------------|---|-----|--|--|

|    | I/O Map Base Address | Reserved     |   | 100 |  |  |

|    | Reserved             |              |   |     |  |  |

|    | Res                  | erved        |   | 92  |  |  |

|    | IST7 (upp            | per 32 bits) |   | 88  |  |  |

|    | IST7 (low            | er 32 bits)  |   | 84  |  |  |

|    | IST6 (upp            | er 32 bits)  |   | 80  |  |  |

|    | IST6 (low            | er 32 bits)  |   | 76  |  |  |

|    | IST5 (upp            | er 32 bits)  |   | 72  |  |  |

|    | IST5 (low            | er 32 bits)  |   | 68  |  |  |

|    | IST4 (upp            | er 32 bits)  |   | 64  |  |  |

|    | IST4 (low            | er 32 bits)  |   | 60  |  |  |

|    | IST3 (upp            | per 32 bits) |   | 56  |  |  |

|    | IST3 (low            | er 32 bits)  |   | 52  |  |  |

|    | IST2 (upp            | er 32 bits)  |   | 48  |  |  |

|    | IST2 (low            | er 32 bits)  |   | 44  |  |  |

|    | IST1 (upp            | er 32 bits)  |   | 40  |  |  |

|    | IST1 (low            | er 32 bits)  |   | 36  |  |  |

|    | Res                  | erved        |   | 32  |  |  |

|    | Res                  | erved        |   | 28  |  |  |

|    | RSP2 (up             | per 32 bits) |   | 24  |  |  |

|    | RSP2 (lov            | ver 32 bits) |   | 20  |  |  |

|    | RSP1 (up             | per 32 bits) |   | 16  |  |  |

|    | RSP1 (lov            | ver 32 bits) |   | 12  |  |  |

|    | RSP0 (up             | per 32 bits) |   | 8   |  |  |

|    | RSP0 (lower 32 bits) |              |   |     |  |  |

|    | Res                  | erved        |   | 0   |  |  |

Reserved bits. Set to 0.

Image. 9: Long-Mode Task State Segment layout (Figure 9-11. 64-Bit TSS Format [1])

| Field                   | Purpose                                                                  |

|-------------------------|--------------------------------------------------------------------------|

| I/O Map Base<br>Address | The 16-bit offset to the I/O permission bit map from the 64-bit TSS base |

| ISTn                    | Interrupt Stack Table (IST) pointers                                     |

| RSPn                    | Stack Pointers (rsp) for privilege levels 0-2                            |

Table. 20: Task State Segment fields (Vol. 3A, Chapter 9.7 Task Management in 64-bit Mode [1])

# 2.6.1 Memory Management Register

To actually use any of the configured memory management data structures, the corresponding registers have to be set. That is because the values contained in the registers allow the CPU to know where the data structures lie in memory.

| Register | Name                                | Value Type                                                                            |

|----------|-------------------------------------|---------------------------------------------------------------------------------------|

| GDTR     | Global Descriptor Table Register    | Descriptor Table Pointer pointing to GDT start address in memory (see Section 2.4.3). |

| IDTR     | Interrupt Descriptor Table Register | Descriptor Table Pointer pointing to IDT start address in memory (see Section 2.4.3). |

| TR       | Task Register                       | Segment Selector pointing to Task State Segment (see Section 2.4.2).                  |

Table. 21: Memory Management Registers (Vol. 3A, Chapter 2.4 Memory-Management Registers [1])

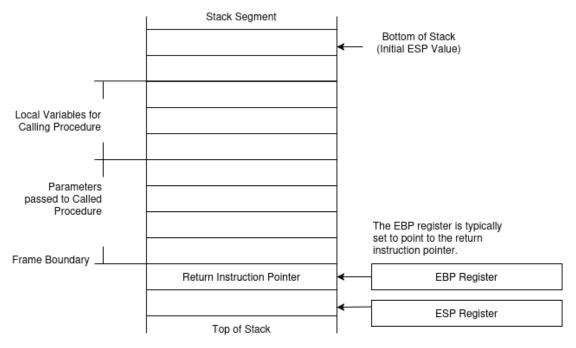

#### 2.7 Procedure Calls

Procedure calls are a mechanism to access kernel functionality from User Mode. Generally there are three different options how such a call can be made. Each comes with its own advantages and disadvantages.

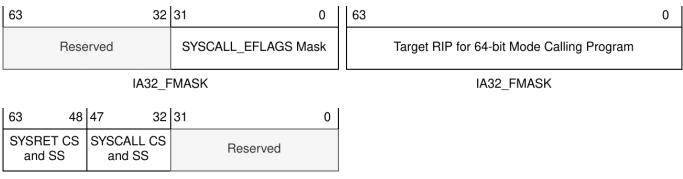

# 2.7.1 SYSCALL / SYSRET

SYSCALL / SYSRET are designed for 64-Bit Mode. SYSCALL is used in privilege level 3 to access operating system procedures, while SYSRET is used in privilege level 0 to return to level 3.

#### **2.7.1.1** Overview

The processor uses certain preconfigured Model Specific Registers (MSR) as configuration on what the SYSCALL / SYSRET instructions actually do. The structure of these registers and how they should be configured can be seen below:

IA32\_STAR

Table. 22: Fast System Calls Registers (Figure 6-14. MSRs Used by SYSCALL and SYSRET [1])

The values in this register is then used differently depending on if the SYSCALL or SYSRET instruction is executed.

| MSR Name   | Usage by SYSCALL                                                                                                                                                                                                                                                                                                               | Usage by SYSRET                                                                                                                                                                                                                                                                                                                                                         |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IA32_FMASK | RFLAGS mask to ignore certain bits. All bit set in the Mask will be disabled if they are currently enabled. RFLAGS & (~IA32_FMASK).                                                                                                                                                                                            | Not used. Instead RFLAGS are saved into R11 register by SYSCALL instruction. Restored when SYSRET instruction is executed into RFLAGS.                                                                                                                                                                                                                                  |

| IA32_LSTAR | Target instruction pointer that will be called on SYSCALL instruction.                                                                                                                                                                                                                                                         | Not used. Instead return function is copied into by SYSCALL instruction. Which will be called when the SYSRET instruction is executed loading the value into RIP.                                                                                                                                                                                                       |

| IA32_STAR  | Uses the Segment Selector that is the SYSCALL CS and SS value, being bits 32:47 of the IA32_STAR as the base for calculations.  • Target Code Segment the SYSCALL will switch into is simply this value.  • Target Stack Segment the SYSCALL will switch into is simply this value + 8, results in Segment Selector Index + 1. | Uses the Segment Selector that is the SYSRET CS and SS value, being bits 48:63 of the IA32_STAR as the base for calculations.  • Target Code Segment the SYSRET will switch into is simply this value + 16, results in Segment Selector Index + 2.  • Target Stack Segment the SYSRET will switch into is simply this value + 8, results in Segment Selector Index + 1. |

Table. 23: Fast System Calls in 64-Bit mode (Vol. 3A, Chapter 6.8.8 Fast System Calls in 64-Bit mode [1])

However, the SYSCALL / SYSRET instructions does not save the Stack Pointer. If the System Call intends to change the stack, this must be done by the operating system. (Vol. 3A, Chapter 6.8.8 Fast System Calls in 64-Bit mode [1])

#### 2.7.1.2 Evaluation of SYSCALL and SYSRET

| Advantages                                                   | Disadvantages                                                                                        |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Specifically designed for fast System Call Entry / Exit      | Does not automatically switch stacks or reload CS and SS registers from the GDT                      |

| Currently the go-to instruction for modern operating systems | Requires IA32_LSTAR, IA32_STAR, and IA32_FMASK Model Specific Registers (MSRs) to be properly set up |

| Automatically stores RIP and RFLAGS                          | Does not save the current Stack Pointer                                                              |

| Lower latency compared to INT n                              | Harder to set up compared to INT n                                                                   |

Table. 24: Advantages and disadvantages of SYSCALL / SYSRET instruction

# 2.7.2 SYSENTER / SYSEXIT

SYSENTER / SYSEXIT are designed for performance. As with the previous companion instructions, SYSENTER is used in privilege level 3 to access operating system procedures and SYSEXIT is used in privilege level 0 to return to level 3. However, these two instructions do not work on x86 on processors by all manufacturers, as they only work on x86\_64 Intel processors.

#### **2.7.2.1** Overview

| MSR Name          | Usage by SYSENTER                                                                                                                                                                                                                                                                            | Usage by SYSEXIT                                                                                                                                                                                                                                                                                                                        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IA32_SYSENTER_CS  | Uses the Segment Selector that is the IA32_SYSENTER_CS value as the base for calculations.  • Target Code Segment the SYSENTER will switch into is simply this value.  • Target Stack Segment the SYSENTER will switch into is simply this value + 8, results in Segment Selector Index + 1. | Uses the Segment Selector that is the IA32_SYSENTER_CS value as the base for calculations.  • Target Code Segment the SYSEXIT will switch into is simply this value + 32, results in Segment Selector Index + 4.  • Target Stack Segment the SYSEXIT will switch into is simply this value + 40, results in Segment Selector Index + 5. |

| IA32_SYSENTER_EIP | Target instruction pointer that will be called on SYSENTER instruction.                                                                                                                                                                                                                      | Not used. Instead return function is copied into by SYSENTER instruction. Which will be called when the SYSEXIT instruction is executed loading the value into RIP.                                                                                                                                                                     |

| IA32_SYSENTER_ESP | Target Stack Pointer that will be loaded on SYSENTER instruction.                                                                                                                                                                                                                            | Not used. Instead the Stack Pointer is copied into by SYSENTER instruction. Which will be loaded into RSP when the SYSEXIT instruction is executed.                                                                                                                                                                                     |

Table. 25: Fast System Calls in 64-Bit mode (Vol. 3A, Chapter 6.8.8 Fast System Calls in 64-Bit mode [1])

During SYSEXIT, the processor loads the new value for the CS register from the same bits as SYSENTER does, but to get the offset to the user Code Segment, it adds 32 to that number. This behavior forces a specific GDT layout, which is showcased in the table below.

| Offset (Hex) | Offset (Dec) | Segment Descriptor  |

|--------------|--------------|---------------------|

| 0x0          | 0            | Null Segment        |

| 0x10         | 16           | Kernel Code Segment |

| 0x20         | 32           | Kernel Data Segment |

| 0x30         | 48           | User Code Segment   |

| 0x40         | 64           | User Data Segment   |

Table. 26: Expected GDT layout by SYSEXIT instruction

#### 2.7.2.2 Evaluation of SYSENTER and SYSEXIT

| Advantages                                              | Disadvantages                                                 |

|---------------------------------------------------------|---------------------------------------------------------------|

| Easy to setup                                           | Only works on Intel processors in 64-bit mode                 |

| Specifically designed for fast System Call Entry / Exit | Not very educational (hides a lot of work from the developer) |

| Lower latency compared to INT 0x80                      |                                                               |

Table. 27: Advantages and disadvantages of SYSENTER / SYSEXIT instructions

# **2.7.3 INT/IRETQ**

In contrast to SYSCALL and SYSENTER, the instruction INT n is not specifically designed to execute operating system procedure calls. INT n exists to send an interrupt signal, which will be handled inside privilege level 3. But exactly due to this behavior, it can be used as a stand-in for SYSCALL / SYSENTER.

#### **2.7.3.1** Overview

The operand n specifies a vector, which essentially is an index to a Gate Descriptor in the IDT. If the INT n instruction is used to handle system calls, the vector 0x80 should be used, as this is the vector used by the Linux kernel. The interrupt service routine (ISR) inside the gate descriptor at index 0x80 is then called and should contain a branching mechanism to determine which type of "SYSCALL" operation is being executed. The System Call type must be specified in the RAX register by the caller.